TSMCは4月22日(米国時間)、米国カリフォルニア州サンタクララで同社の顧客向けイベント「TSMC 2026 North America Technology Symposium (2026年 TSMC北米テクノロジーシンポジウム)」を開催した。今後数ヶ月にわたり世界各地で開催される一連の顧客向けイベントの幕開けとして、今回は「Expanding AI with Leadership Silicon(リーダーシップ・シリコンでAIを拡大する)」をテーマとし、同社の今後の技術開発とファウンドリサービスの方向性などが語られた。

先端ロジック技術のロードマップを更新、「A13/A12」プロセスを発表

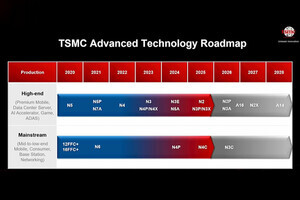

TSMCは今回、先端ロジックプロセスのロードマップを更新し、新たに「A13プロセス(いわゆる1.3nmプロセス)」および「A12(同1.2nm)プロセス」を発表した。さらにはN2についても、そのトランジスタ密度向上・性能向上版である「N2Uプロセス」を発表した。

A14のシュリンク版となる「A13」

A13プロセス技術は、2025年に発表されたA14をベースにシュリンクしたもので、次世代人工知能(AI)、高性能コンピューティング(HPC)、モバイルアプリケーションにおける計算能力に対する顧客の飽くなき需要に対応するため、従来以上に小型かつ効率的な設計を可能にするとしている。

A14プロセスと比較して寸法を0.97倍に縮小することで面積を6%削減しつつ、設計ルールはA14と完全な互換性を持たせることで、顧客は設計を容易にA14からA13に移行させることができるとする。さらに、設計とプロセス技術の同時最適化(DTCO)により電力効率と性能を向上させることができるともする。量産開始は、A14の量産開始年である2028年の1年後となる2029年からを予定している。

TSMC会長兼CEOのC.C. Wei氏は、「顧客は常に次のイノベーションを見据え、A13のような信頼性の高い新しいシリコン技術を求めている。これらの技術は、顧客が革新的な設計を必要とするまさにその時に、大量生産に対応できるよう綿密に準備している。TSMCの先進的なプロセス技術は、密度、性能、電力効率において業界をリードしており、顧客の将来の製品のために、これらの技術をさらに向上させるべく継続的に努力している。そして顧客にとってもっとも信頼できる技術パートナーとして、顧客の成功を確実なものにしていく」と述べている。

裏面電力供給を採用する「A12」と進化版2nm「N2U」も投入

A13に加え、AIおよびHPCアプリケーション向けに背面からの電力供給を実現する「Super Power Rail (SPR)(裏面電力供給)技術」を採用したA14拡張版となる「A12」も発表した。A12もA13同様、2029年からの量産開始を予定している。

さらに、2nmプラットフォームの発展版となる「N2U」も発表した。N2Uは、設計と技術の協調最適化により、N2Pと比較して3~4%の速度向上、または8~10%の消費電力削減、そして1.02~1.03倍のロジック密度向上を実現するという。2nmプラットフォームのプロセス成熟度と高い歩留まり性能を活かし、AI、HPC、モバイルアプリケーション向けにバランスの取れた選択肢として提供され、2028年からの量産開始を予定している。

裏面電力供給のA16は2027年に延期

A12の前に、TSMC初となるSPRを採用したA16プロセスに関しては、2025年の発表の際は2026年後半から量産開始するとしていたが、今回示されたロードマップでは2027年へと移動でしている。

複雑な信号回路網や高密度の電源供給網のあるHPC製品に最適なプロセスになるとTSMCは説明しており、N2Pと比較して、同一Vddで速度が8~10%向上し、同一速度なら消費電力が15~20%減少、チップ密度は1.07~1.10倍となるとする。

14レチクルサイズのCoWoSは2028年より生産開始、2029年には40レチクルサイズに対応

このほかTSMCは、単一パッケージ内でより多くの演算能力とメモリを必要とするAI需要に対応するため、チップ・オン・ウェハ・オン・サブストレート(CoWoS)技術の拡張を続け、より多くのシリコンチップを集積しようとしている。

現在、同社は5.5レチクルサイズのCoWoSを生産しており、さらに大型バージョンの開発も計画している。約10個の大型演算ダイと20個のHBMスタックを集積できる14レチクルサイズのCoWoSは、2028年に生産を開始する予定としているほか、2029年には14レチクルを超えるサイズへの拡張も予定されている。これらの新製品は、AIの演算スケーリングに関して顧客により多くの選択肢を提供するとともに、2029年に提供開始予定のTSMCの40レチクルサイズのSoW-X(システム・オン・ウェハ技術)を補完するものと位置付けられている。

TSMCは、最先端の技術プラットフォーム上でTSMC-SoIC 3Dチップ積層技術も提供しており、A14-to-A14 SoICは2029年に量産開始予定である。これにより、N2-on-N2 SoICと比較してダイ間I/O密度が1.8倍向上し、積層チップ間のデータ転送帯域幅が向上するという。

COUPEをパッケージ内に直接集積で電力効率2倍、レイテンシ1/10に

TSMCのコンパクト・ユニバーサル・フォトニックエンジン(TSMC-COUPE)は、2026年に生産開始予定のコパッケージド・オプティックス(CPO)ソリューションで重要なマイルストーンを達成する見込みである。

COUPEをパッケージ内部に直接集積することで、TSMCは回路基板上のプラグイン式バージョンのCu配線と比較して、電力効率を2倍増加させ、レイテンシを1/10に削減する。この技術は、データセンターのラック間でデータを転送するための、非常にコンパクトでエネルギー効率の高いソリューションである200Gbpsマイクロリング変調器に採用されるとする。

車載グレードN2Aプロセスは2028年にAEC-Q100認証を取得予定

先進運転支援システム(ADAS)や自動運転車には、最先端技術による高い演算性能に加え、厳格な品質・信頼性基準が求められているほか、ヒューマノイドロボットなどのフィジカルAIアプリケーションも同様に厳しい要件が課せられている。

こうしたニーズに応えるため、TSMCはナノシートトランジスタを採用した初の車載グレードプロセス技術である「N2A」を正式発表した。N2Aは、N3Aと比較して消費電力は同等ながら15~20%向上し、2028年にはAEC-Q100認証を取得する予定である。同社ではN2Pプロセス設計キット(PDK)の一部として「車載用途」設計キットを提供することで、N2Aプロセスが完全に認証される前に、顧客は早期に車載向け設計を開始できるようになると説明している。

TSMCが自動車製品の開発サイクルを加速させるための取り組みは、これまでも推進されてきており、2026年に量産が開始されるN3Aでは、2023年よりN3「Auto Early」プログラムに基づく形で設計を開始することができ、すでに10以上の製品がN3A技術に基づいた形で計画されるなど、自動車をよりスマートに、より環境に優しく、より安全にする取り組みが進められている。

ディスプレイドライバ向けに高電圧プロセス「N16HV」も導入

このほかTSMCは、ディスプレイドライバ用途向けに「N16HV」プロセスを開発し、2026年に投入するとしている。これにより同社はFinFETプロセスに高電圧技術を導入する業界初の企業となる。スマートフォン向けディスプレイドライバの場合、N16HVは従来のN28HVプロセスと比較してゲート密度を41%向上させ、消費電力を35%削減するほか、ニアアイ・ディスプレイの場合、N16HVはダイ面積を40%縮小し、消費電力を20%以上削減できるようになるとしている。

今回の発表を見渡すと、N2U、A13やA12といったプロセス微細化による「小型化」と、先進的な大規模パッケージングによる「大型化」を並行して推進することにより、AI時代の要求を満たすことを目指す戦略を明確にしたといえる。

高NA EUV露光装置はA13/12では未だ使わない

なお、同社Co-COO兼事業開発・グローバル営業担当上級副社長(SVP)のケビン・チャン氏は、A13およびA12について、「R&Dチームの努力で、いずれも高価な高NA EUV露光装置を用いずに製造できることとなった」と述べている。「Intel 14A(いわゆる1.4nm相当)」プロセスから高NA EUV露光装置の採用を決めたIntelとは対照的な判断である。同氏によれば「自社R&Dチームは、高NAを使用せずに技術スケーリングを推進する方法を見つけ続けている。高NA技術はいつかは使用しなければならないかもしれないが、現時点では、高価な高NA EUVに移行しなくても従来のEUVで対応できる」と述べており、高額な高NA EUV露光装置を量産向け投資として導入しないで済むのであれば、その分、投資コストを抑えることができるようになることから、TSMCが競合に対してA13/A12世代における製造コストで優位に立つ可能性がある。