TSMCは6月11日、日本で年次イベント「TSMC 2025 Japan Technology Symposium」を開催し、同社の先端プロセスや先端パッケージ、スペシャリティプロセスなどについての最新の取り組み状況などの解説を行った。

開催の挨拶に立った、TSMCジャパン代表取締役社長の小野寺誠氏は、今回のテーマを「ADVANCING THE AI FUTURE」を説明。AIが新たな発見の時代の原動力となることを強調した。

2024年にはノーベル賞受賞の研究対象にもなるなど、現在、生成AIのみならず、さまざまな分野でAIの活用が進められているが、そうした中でもAIは日々進化を続けており、そうした状況を同氏は「AI EVOLUTION」と表現する。

AIの活用の仕方についても、AIエージェントが登場しつつある現状の先には、ロボットや自動車がインテリジェント化を果たすフィジカルAIの世界が待っており、2050年には40億台のAIロボットが活躍し、そのうち6億5000万台が人型ロボットになるという試算もあり、市場規模としても2030年までにAIロボットだけで350億ドル以上に成長すると期待されているとする。

また、ありとあらゆるものにAI機能が搭載されるようになると、エッジでのAI活用が重要になってくる。そうした、AIの民主化の時代には、より高度な計算力とバッテリーを長寿命化するエネルギー効率の向上が重要であり、そのためにはより微細なトランジスタの実現による低コスト化が重要になると同氏は説明する。

「TSMCは、先端プロセスとヘテロジニアスでのイノベーションを推し進めており、より小型で高性能なトランジスタを実現するプロセスの微細化を推進してきたほか、飽くなき需要を満たすためにチップレットと3D ICも提供し、持続可能な社会の実現を支援してきた」(同)とし、AIの普及促進を支援し、すべての人にAIの恩恵がもたらさせるようにパートナー各社と協力していくという。

日本でも存在感を増すTSMC

AI半導体の活用をはじめとして、先端プロセスを提供できる半導体メーカーが不在の日本においてTSMCに製造委託するといった流れが近年、加速度的に増加しているという。

その結果、国内市場の売り上げは1997年には1億5000万ドルほどであったものが、2024年には43億ドルまで成長。累計で1219万1000枚(300mm換算)のウェハが日本の顧客向けに出荷されてきたが、2024年だけでも149万枚が供給されたという。

また、テープアウト数も累計で2619件に到達したほか、LSI試作サービスで、1枚のウェハ上に複数の回路デザインを搭載する「TSMC CyberShuttle(サイバーシャトル)」も2145件、そのうち1510件がアカデミープログラムを利用したもので、国内47大学が活用してきたとする。

このほか、近年、日本でも3D IC研究センターや大阪でのデザインセンターの開設を進めてきたほか、2024年には熊本のJASM第1工場が稼働を開始。熊本第2工場も2025年後半より建設を開始する予定だが、同社にも2025年4月に新入社員として527名が入社しており、従業員規模は約2400名へと拡大したという。

AIがけん引する今後の半導体市場

代わって基調講演に登壇したTSMCシニア・バイス・プレジデント 兼 副共同最高業務執行責任者のKevin Zhang(ケビン・ジャン)氏は、「Strong AI Data Center Demand」と表現し、どこに行ってもAIの話で持ちきりであることを指摘。「30年以上にわたって半導体業界に居るが、ここまで興奮する時代はなかった。AIがそういう時代をもたらした」とAIが半導体業界の在り方そのものを変えようとしていることを強調した。

実際、同社の業績を各月で見ると、2024年の2月以降、前年同月比で2桁成長を16か月連続(2025年5月の単月決算発表時点までで算出)持続させている。同氏も、2024年初頭からAIの需要が半導体業界を抜本的に変えるような動きを見せてきており、2025年も非常に需要が強い状況が続いていることに言及。その成長の背景には、同社が提供する5nm以下の先端プロセスの存在と6nm RFプロセス、そして先端パッケージ技術であるCoWoSの存在があるとする。

2025年の半導体市場規模について同社では前年比10%ほどの成長率を見込んでいるが、そのけん引役はAIであり、2030年の半導体市場1兆ドルという予測についても、そのうちの45%をHPC/AIが占めるとみている(そのほか、スマートフォン25%、自動車15%、IoT10%など)。

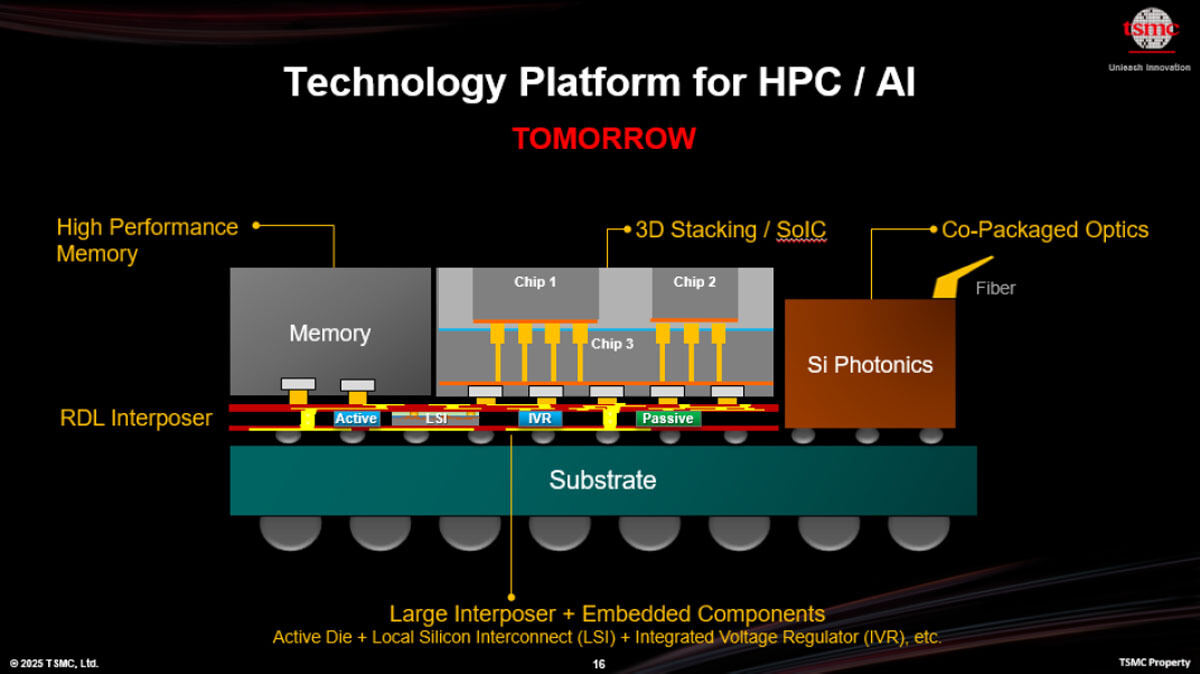

そうしたAIの高性能化を支える基盤となるのが同社のCoWoSであるが、現在のシリコンサブストレートの上にインターポーザがあり、SoCとHBMが搭載されるという形だけではなく、将来はサブストレートの上に樹脂基板を用いたRDL(Redistribution Layer Interposer)インターポーザを接続し、その上に3DベースのSoCやメモリ、そしてシリコンフォトニクスを活用したCPO(Co-Packaged Optics)へと進化していくことが期待されている。

自動車分野もソフトウェア・デファインド・ビークル(SDV)の潮流で、高性能なセントラルコンピューティングを実現するために先端プロセスを活用する必要が生じてくるが、同社ではこうした取り組みをシリコン・デファインドと表現。さらにその先にあるフィジカルAIとして注目される人型ロボットには、セントラルコンピューティングとしてのより多くのLLMやLMMを処理するためのアプリケーションプロセッサやコネクティビティ、各マニュピレータ制御のためのマイコンやモーターコントロール、状況認識のためのCMOSイメージセンサやMEMSマイク、レーダー/LiDAR、電力制御のためのPMIC、バッテリー制御IC、充電管理ICなどが必要となり、こうしたニーズが今後の半導体需要をけん引していく存在になるとする。

また、期待されつつも今一つ市場が大きく拡大しないXRゴーグル/グラス市場についても、「今の問題は重いということ」とし、サイズ、重量、エネルギー効率などの面で10倍の改善が必要とし、その実現には先端プロセスの進化が必要になってくると、今後も社会の発展のためにはプロセスの微細化が重要であることに変わりはないことを強調した。

2025年に立ち上がる2nmプロセスの影で3年目の進化を遂げる3nmプロセス

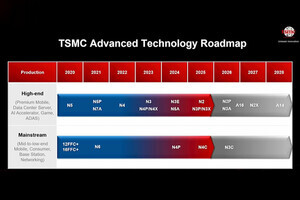

こうした先端プロセスの進化は毎年継続して行われており、2025年後半には2nmプロセスの第1世代(N2)が提供開始される予定。現状で256MビットSRAMの平均歩留まりが90%以上を達成しており、その新規テープアウト数は提供1年目で比べると5nm(N5)比で2倍、2年目の新規テープアウト数になるとN5比で4倍に増加。「(N5と比べて)より多くの顧客が活用している」(同)とする。

さらに、2026年後半には第2世代2nmプロセスとなる「N2P」も量産を開始する計画。N2Pは、2023年より提供を開始した3nmの第2世代プロセス「N3E」比で同じ電力であれば最大18%の速度向上、同じ速度であれば約36%の電力削減、そしてロジック密度は1.2倍に向上されるという。また、最大動作周波数を約10%向上させた「N2X」が2027年に量産を開始する予定ともしている。

一方で最後にして最高のFinFETプロセスと同氏が評する3nmプロセスについてもN3EがフラッグシップモバイルおよびHPC/AI向けに量産提供済みだが、2024年第4四半期には第3世代の「N3P」も量産を開始したとする。2025年にも3年目の3nmプロセスの進化として、CPUの高性能化などのニーズに対応する「N3X」ならびにコスト重視ニーズに対応する「N3C」の提供が行われるほか、自動車アプリケーション向け先端プロセスとなる「N3A」も提供される予定で、現在、最終的な品質改善を実施中で、AEC-Q100 Grade1認証取得に向けて取り組んでおり、2025年後半にも量産の準備が整い、2026年には提供できる予定だとしている。

さらに、2026年後半には、より微細なプロセスとなる1.6nmプロセス「A16」の量産開始も予定されている。A16は、同社として初めて「Super Power Rail(SPR)」と呼ぶ背面電力供給技術(BSPDN:Back Side Power Delivery Network)が採用され、データセンター向けAI/HPC製品が求める厳格な信号配線および電力供給要件に対応することを可能にするとしている。

加えて、2028年の量産開始予定として、さらに微細な1.4nmプロセス「A14」の研究開発も進められている。A14はN2比で同じ電力で最大15%の速度向上、同じ速度で最大30%の電力削減、そしてロジック密度は20%以上の向上を計画しており、NanoFlexスタンダードセルアーキテクチャをNanoFlex Proへと進化させることで、より性能、電力効率、設計柔軟性の向上を図るとしている(SPR版は2029年の提供開始予定)。

デバイスのアーキテクチャの進化とチップレベルでのインテグレーションの進化

N2プロセスでは、トランジスタ構造がそれまでのFinFETからナノシートトランジスタ(Gate-All-Around FET:GAA)へと変更されるが、その先のアーキテクチャとしてCFETの研究開発も進められている。

CFETはpFETとnFETを垂直に重ねることでほぼ2倍の密度を実現する技術。2024年のIEDMにおいて同社はゲートピッチ48nmのCFETインバータを発表済みである。

また、その先の技術、いわゆるBeyond Siとして同社では2つの方向性を示している。2つは2D化合物材料である2D TMD(遷移金属ダイカルコゲナイド)の活用。もう1つがCNT(カーボンナノチューブ)を活用したトランジスタ形成である。同氏は「3次元から次元を下げて2次元や1次元とすることで今後も高性能化を図っていくことができるようになる」と説明する。

一方のチップレベルのインテグレーション技術としては、シリコンダイを3次元積層する技術である「SoIC(System on Integrated Chips)」と、それを活用したCoWoSパッケージ技術の進化を挙げている。

「トランジスタの進化だけではAIのニーズに対応できなくなってきており、高度なインテグレーションが必要となっている。そのためにSoICは重要な技術となる」(同)とする。

2025年には6μmピッチ/1レチクルのN3-on-N4のSoICが量産開始の予定で、次世代となるA14-on-N2 SoICについては2029年に提供予定としている。

また、CoWoSについてもレチクルサイズの大型化により、1パッケージ内により多くのチップを統合することができるようになり、複数のチップレットやHBMなどのメモリスタックを効率的に集積できるようになることから、技術開発が進められており、現状が3.3レチクルサイズだが、2026年には5.5レチクルサイズのRDLインターポーザベースのCoWoS-Lへと進化を予定しているほか、2027年には9.5レチクルサイズのCoWoSの量産も計画。このサイズまで拡大すると、12個以上のHBMスタックと先端ロジックの統合が可能になり、よりAIアクセラレータの大規模化が可能になるという。

さらに、CoWoSベースのウェハサイズのパッケージ技術となる「System-on-Wafer(SoW-X)」の開発も進められている。これは、現行のCoWoSソリューションの40倍の演算性能を持たせることが可能になる技術で、ロジックとHBMの統合だけでなく、コネクタ、電源モジュール、冷却モジュールなど、必要なコンポーネントすべてを一体化できるという。同社では2027年の量産を予定しているとする。

スペシャリティプロセスも進化

このほか、先端プロセス以外のスペシャリティプロセスの進化も同社は推進している。例えばBCDプロセス。同プロセスには2つのトレンドがあるとしており、1つは電圧の向上だとする。これへの対応としては180nm BCDプロセスの100V対応を進めるとしており、これにより産業機器や自動車などで進む48Vシステムのサポートを可能にするという。もう1つは、多くの演算能力をPMICに搭載したいというニーズ。こちらについては28nm BCD+プロセスなど、より微細なプロセスといった方向性を示している。

一定の用途に特化する形のスペシャリティプロセスにもさまざまなニーズが出てきており、BCDプロセスのほかにも、シリコンフォトニクス技術を活用して、将来的には電子ダイとフォトニックダイの積層による高密度な接続とシステムとしての消費電力低減を目指している。これにより、ボードレベルからインタポーザレベルへのオプティカルエンジン(OE)の統合により、電力効率は最終的に10倍以上の向上を図ることができるようになるとする。

また、こうしたパッケージ技術として、基板上の電源管理チップとして、従来技術比で垂直電力密度を5倍に向上させた統合型電圧レギュレータ(IVR)などの開発も進めているとする。

自動車分野ではSDV化による高性能SoCに注目が集まりがちだが、周辺状況を認識するためのCMOSイメージセンサ技術も進化させている。SoC向けとしては、現行のN7AからN5A、そしてN3Aへと進化に向かっているが、CMOSイメージセンサとして、横型オーバーフロー統合コンデンサ(LOFIC:Lateral Overflow Integration Capacitor)技術を活用することでピクセルサイズを小型化しながらも100dB以上のダイナミックレンジを確保できるようになってきたとする。

このほか、車載にも活用できるeNVM技術として、RRAMおよびMRAMの研究開発も進めており、28nm RRAMはすでに車載用途としての認証済みで、12nm RRAMについても車載要件を満たす見込みだとしている。一方もMRAMについても22nm MRAMについてはすでに量産中で、16nm MRAMは顧客対応準備済み、12nm MRAMは研究開発を進めている段階だとしており、いずれについても5nmおよび6nmへのスケーラビリティを目指した研究開発を行っているとしている。

エッジ/IoTで重要となる低消費電力化についても、ウルトラローパワープラットフォームとして、しきい値電圧を0.4Vまで引き下げたN4eプロセスの試験的開発を開始。同プロセスでは、超低リークSRAMとロジックによるリーク電流の抑制により、バッテリー寿命の延長が可能になるとしている。

なお、同氏はAI時代において重要なのはエネルギー効率と演算能力の向上の両立としており、今後も引き続き、パートナーとともにリーダーシップを取ることができる技術の提供を、プラットフォームソリューションとして提供していくことで、顧客ならびに社会のイノベーションをサポートしていくとしていた。