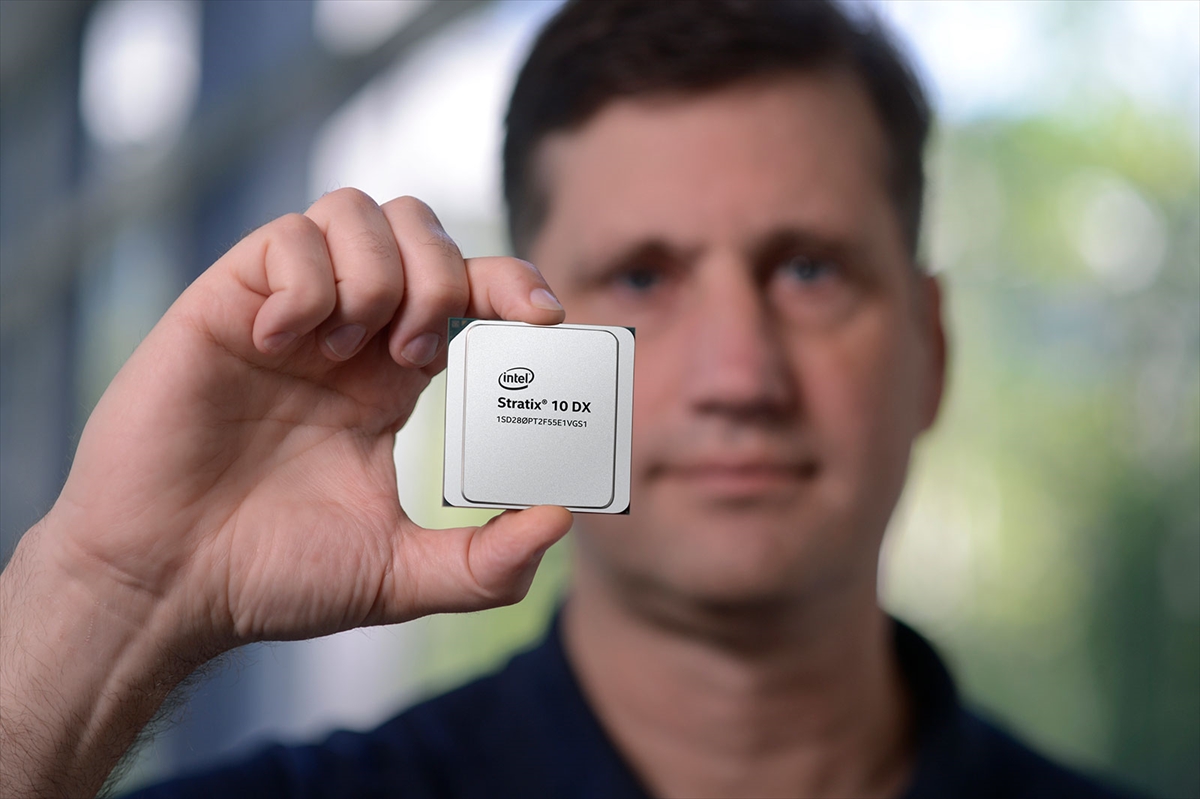

Intelは9月19日(米国時間)、「Stratix 10 DX FPGA」の出荷を発表した(Photo01)が、それに併せて説明会を電話会議の形で開催したので、その模様をお届けする。

-

Photo01:Intel提供の製品写真。ちなみに後ろの男性は発表者のDorsey氏ご本人。(2019年9月24日追記:記事掲載当初「ちなみに後ろの男性は発表者のDorsey氏とは無関係」と書いたところ、Dorsey氏ご本人であるということが確認されましたので、当該箇所を修正させていただきました。関係者ならびに読者の皆様にご迷惑おかけしましたことを深くお詫び申し上げます)

ちなみに説明を行ったのは2019年4月に開催された日本でのAgilex FPGAの説明会の際に来日したPatrick Dorsey氏である。そのDorsey氏、組織変更の関係で肩書が2019年9月現在はVP Product Marketing, FPGA and Power Products, Intel Network and Custom Logic Groupに変更となったそうである。

さてそのStratix 10 DXであるが、これはStratix 10シリーズとしては5つ目の製品ファミリとなる。ラフに言えばStrarix 10 GX/SXが汎用向けで、違いはSXがCortex-A53コアを搭載したSoCという事となる(GXはFPGA Fabricのみ)。また、Stratix 10 TXがネットワーク向けにPHYや100G EtherのハードIPを搭載した製品、Stratix 10 MXがStratix 10 GXにHBM2を搭載したような構成となっている。

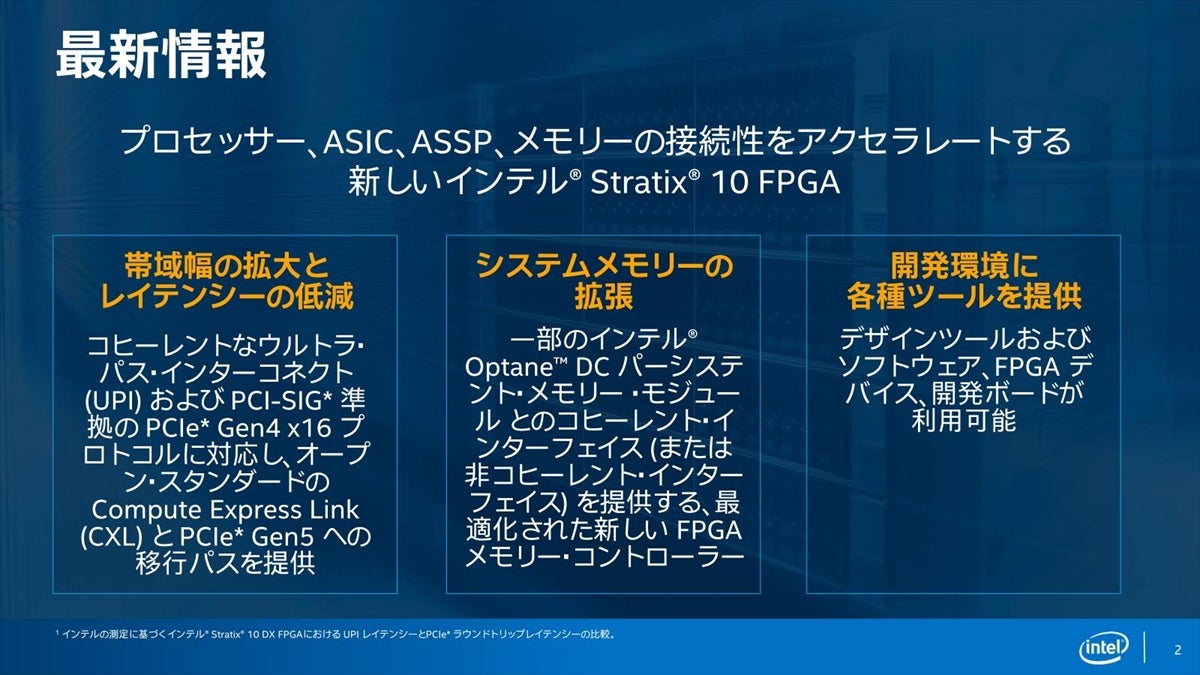

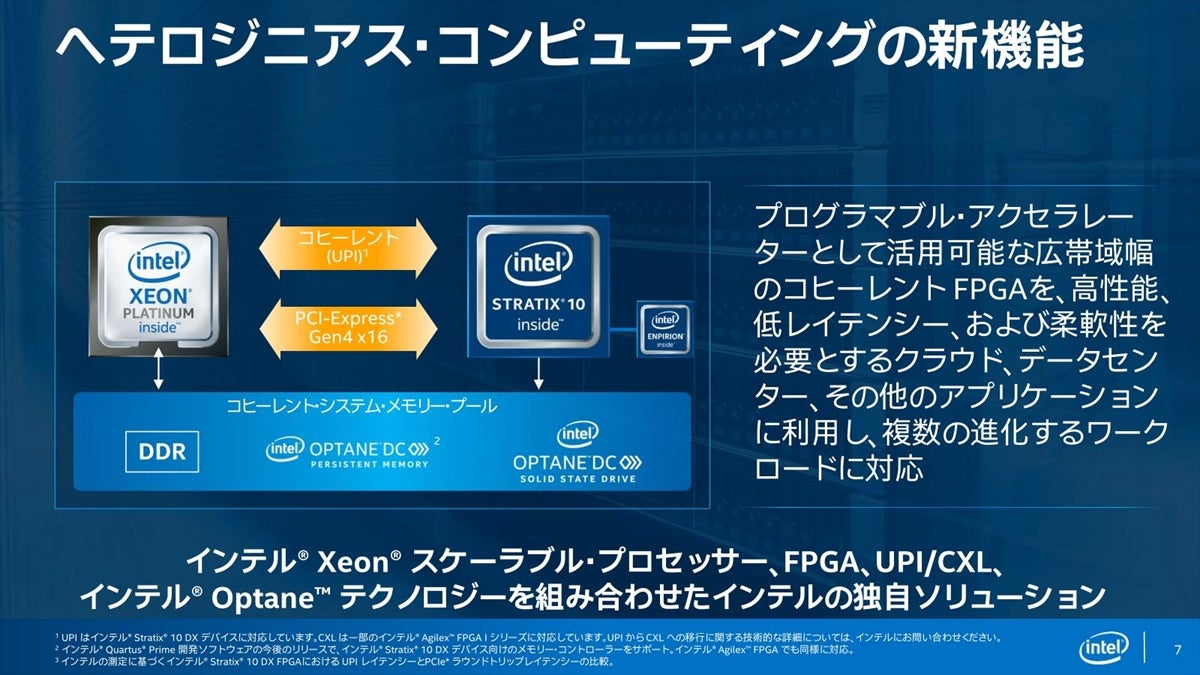

ではStratix 10 DXは? というと、実は何気にロジックエレメント(LE)の規模もほかの製品ファミリよりも大きい上にHBM2を搭載することも可能であるが、最大の特長はホストとのコネクティビティが強化された点にある(Photo02)。

IntelのFPGAとしては初めてPCI Express Gen4(PCIe Gen4)に対応したのみならず、UPI(Ultra Path Interconnect)に対応した(CPU以外としては)初めての製品である。また2chのDIMMソケットを利用可能で、ここに同社のOptane DC Persistent Memoryを搭載することも可能とされる(Photo03)。

-

Photo03:これもIntel提供の評価ボードだが、これはまだ正式なものではなく、Intel社内あるいはISVの開発用に提供しているものらしい。説明は無いが、カード後端のコネクタがUPIと思われる。それにしても物凄い位置にDIMMスロットがあるものである

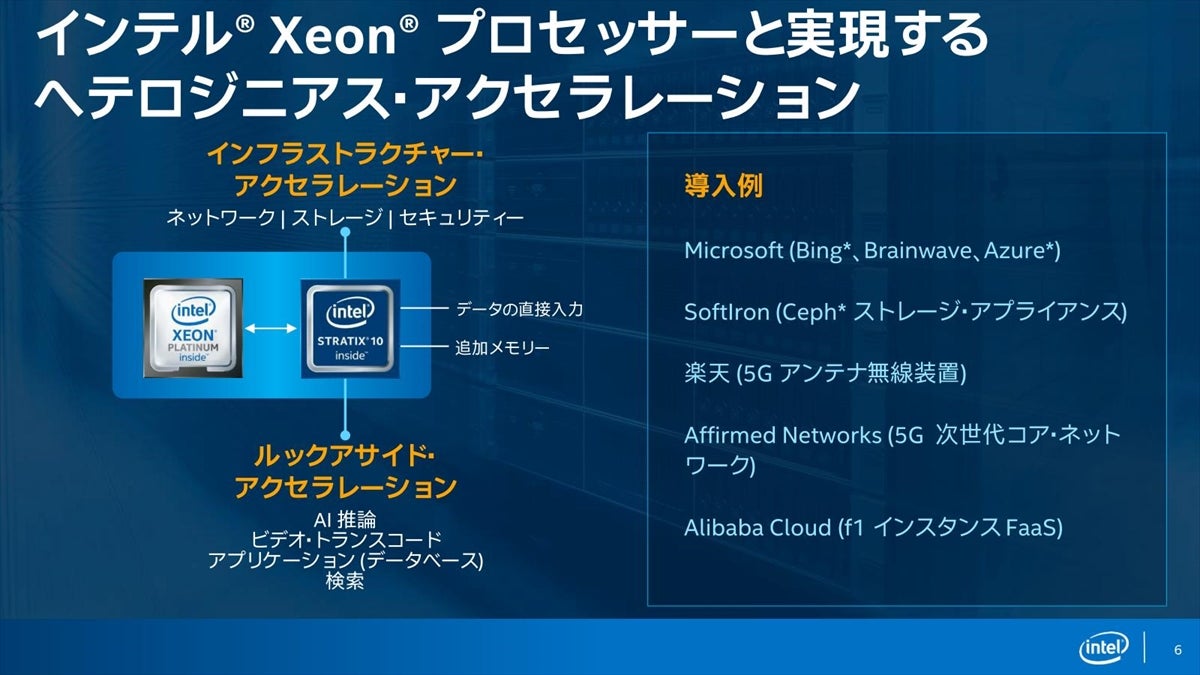

このStratix 10 DXであるが、LE数はローエンドのDX 1100で1325K、ハイエンドのDX 2800で2753Kと結構な数が搭載されている。またStratix 10 TXほどではないが、100G Ethernetに向けた58G PAM4 PHYも搭載されたほか、PCIe Gen4 x16とUPIを合計3chまで利用できるなどコネクティビティが充実しており、それもありIntelとしてはInfrastructure AccelerationとLookaside Accelerationの両方に利用できる、としている(Photo04)。

さて、最大の特長であるPCIe Gen4とUPIの搭載だが、UPIはQPI(Quick Path Interconnect)の後継で、要するにIntelのCPU(主にXeon)同士の接続に利用されるものである。UPIそのものはIntelのXeon Scalable(というか、Skylake-SP)にあわせて登場したもので、当然ながら双方向のCache Coherencyを確保できることになる。これはStratix 10 DXにも当てはまり、UPIを使ってホスト(Xeon)と接続した場合、

- ホストから、FPGA側のMemoryをCache Coherencyを保ってアクセス

- FPGAから、ホスト側のMemoryをCache Coherencyを保ってアクセス

の両方が可能であり、また実際FPGAのアプリケーションでこうしたアクセスを行う事が可能であるとする。

またFPGA側のLocal MemoryとしてHBM2およびDDR4に加え、Optane DC Persistent Memoryをサポートしており、大容量の外部メモリとして利用できるとしている。ただOptane DC Persistent Memoryは、単純に大容量のDRAMとして使う以外に、DRAMエリアとOptane DCエリアを区別して使う方法もあるが、Stratix 10 DXからこうした使い分けが可能になるのか? は現時点でははっきりしない。

-

Photo05:ちなみにサポートされる外部メモリそのものはDDR4/DDR3/DDR2/QDR II+/RLDRAM II/RLDRAM 3と多岐におよんでいるが、Photo03を見る限り普通はDDR4が前提になっている模様

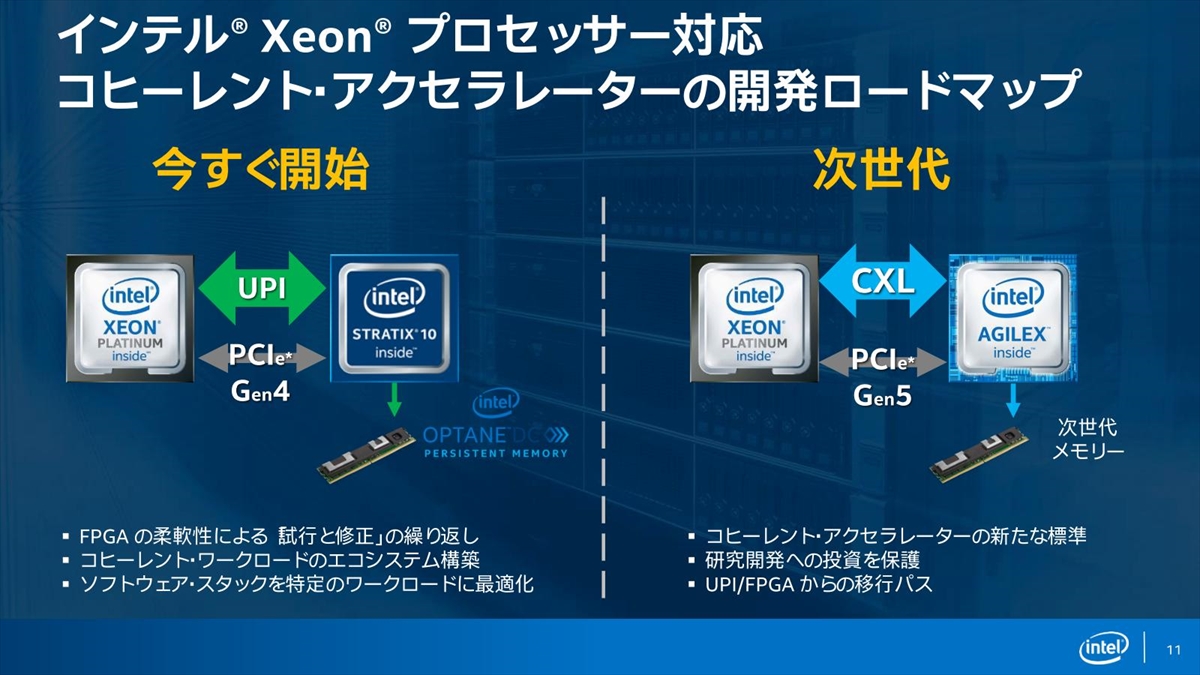

面白いのは今後の展開である。IntelはStratix 10 DXを、Agilexに続くものと位置付けている(Photo06)。Agilexは既報の通りCXLを利用してCPUとのCache Coherencyが利用できるが、これを先取りする形だ。

-

Photo06:「この図だと現在PCIe Gen4が使えるように見えるが、今のXeonはGen3どまりでは?」と突っ込んだところ「将来のXeonはGen4をサポートする(が、それが何時登場するかは言えない)。それとは別に例えばテスターとか組込機器などではPCIe Gen4が利用できるし、そうしたものとStratix 10 DXはPCIe Gen4でつながる」との返事をいただいた

先の話につながるが、UPIを利用する場合、ホスト側とFPGA側の両方にCache AgentやMemory Agentなどが動き、これを利用してCache Coherencyを実現する形になる。何のことは無く、CXLの内部メカニズムにかなり近いものが用意される模様だ。実際CXLとUPIベースのCache Coherencyについて「コード互換性そのものは無いが、ベースとなるメカニズムは同一であり、なので多少の書き換えは必要になるが、UPIベースのアプリケーションは(Agilex上の)CXLベースに移行できる」という話であった。恐らく、CXLで言うところのType 2に近い構成になっているのだと考えられる。

逆に、Agilex世代ではUPIを利用するソリューションは無いのか確認したところ、「今のところは無いが、Agilexはモジュラタイプの構成なので、UPIを搭載することは(技術的には)可能」という話だった。逆に言えば、Stratix 10の将来のバージョンがCXLをサポートすることも、技術的には不可能ではないのだろう(そういう商品計画があるとは思えないが)。

ついでに付け加えておけば、UPIに関しては、特にこれをサポートするカードエッジコネクタなどはないため、基板上に直付けしてXeonのSocketとつなぐという形になる(つまりPACカードの構成だとPCIeのみの接続となる)が、例えばXeonとStratix 10 DXを両方搭載したMCM(いわゆるドーターカードの形式だろう)はあるし、また独自のUPIコネクタを利用するカード(先のPhoto03の右端が恐らくこれである)も存在するという話であった。

このあたりに標準品が使えるのはCXLの世代で、こちらはPCIe Gen5のカードエッジコネクタを共用する形になるので、今慌ててUPIの標準コネクタとかを制定したところで、一時的に使われて終わるだけになる。であれば、この世代は独自規格のままで構わない、という判断なのだろうと思われる。

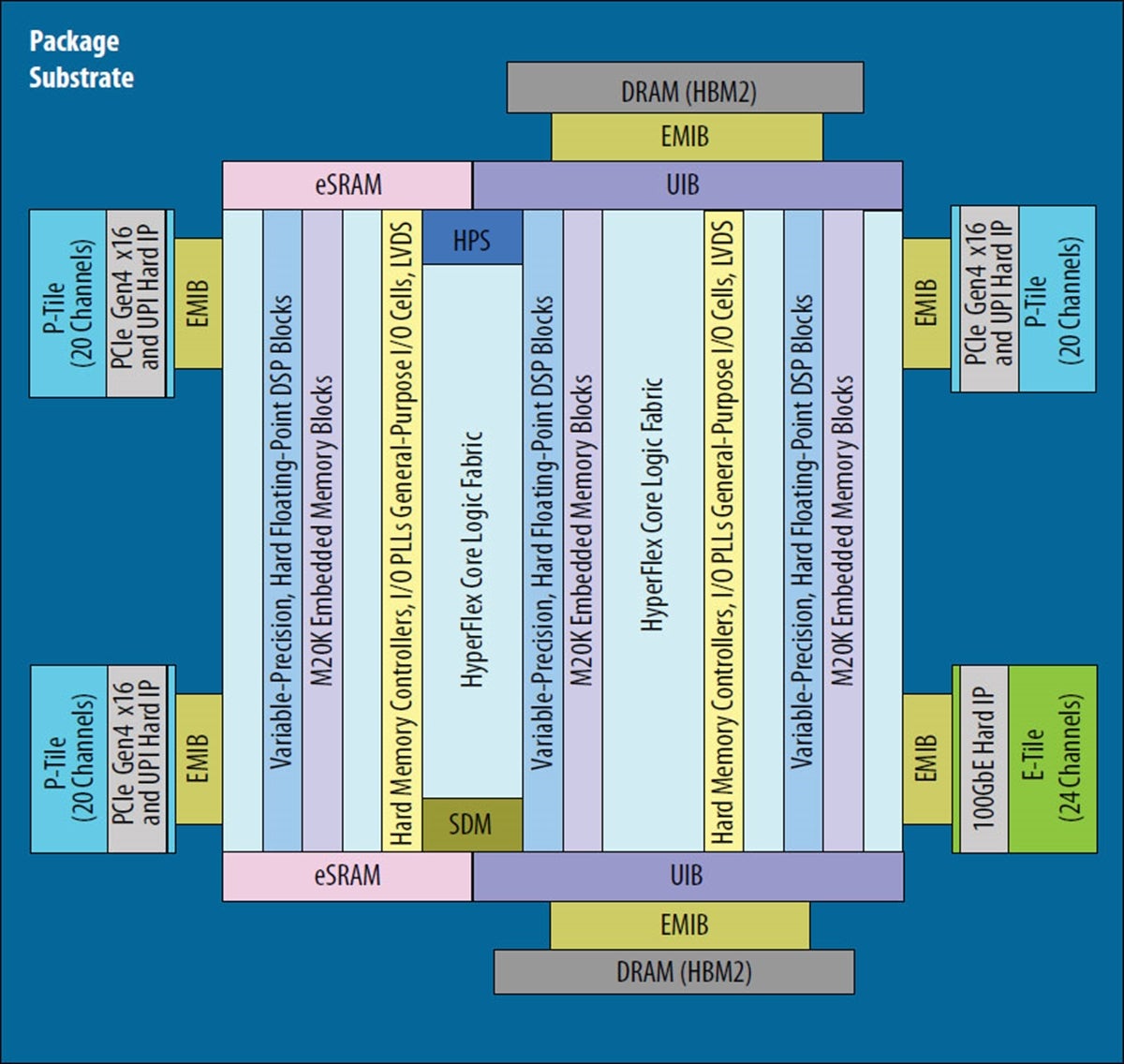

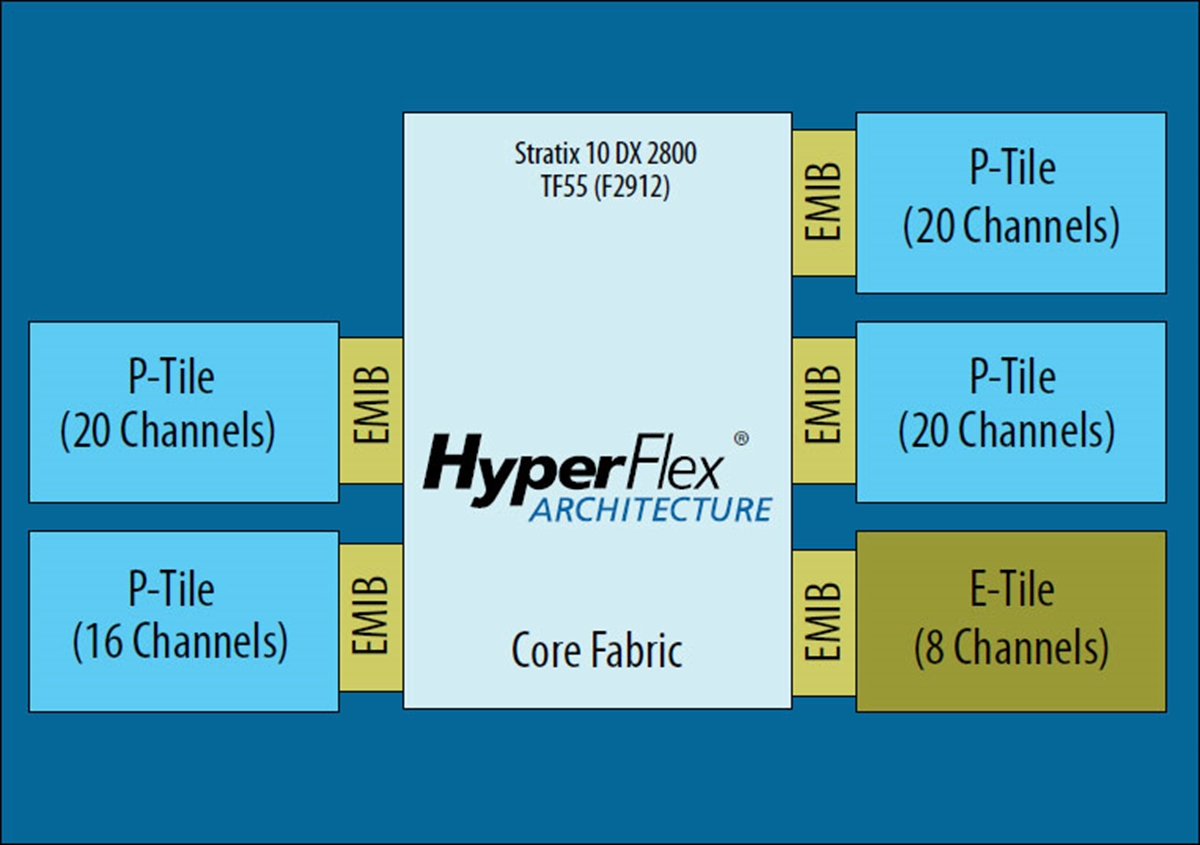

記者説明会で判明した内容は以上であるが、もう少しだけ補足しておく。Stratix 10 DXは現状3製品がラインアップされているが、この構成は全部異なっている。Photo07がStratix 10 DX全体の構成で、中央のLEの周辺に高速なPHYとHBM2が外付け(EMIB経由での接続)される形だ。このPHYは、

- E-Tile:最大24chのSerDesと100G EthernetのHard IPを内蔵

- P-Tile:最大20chのSerDesと、PCIe Gen4およびUPIのHard IPを内蔵

の2種類がある。

ちなみにHPSというのは4コアCortex-A53、SDMはSecure Device Manager、eSRAMはEmbedded SRAm、UIBはUniversal Interface Busの略である。

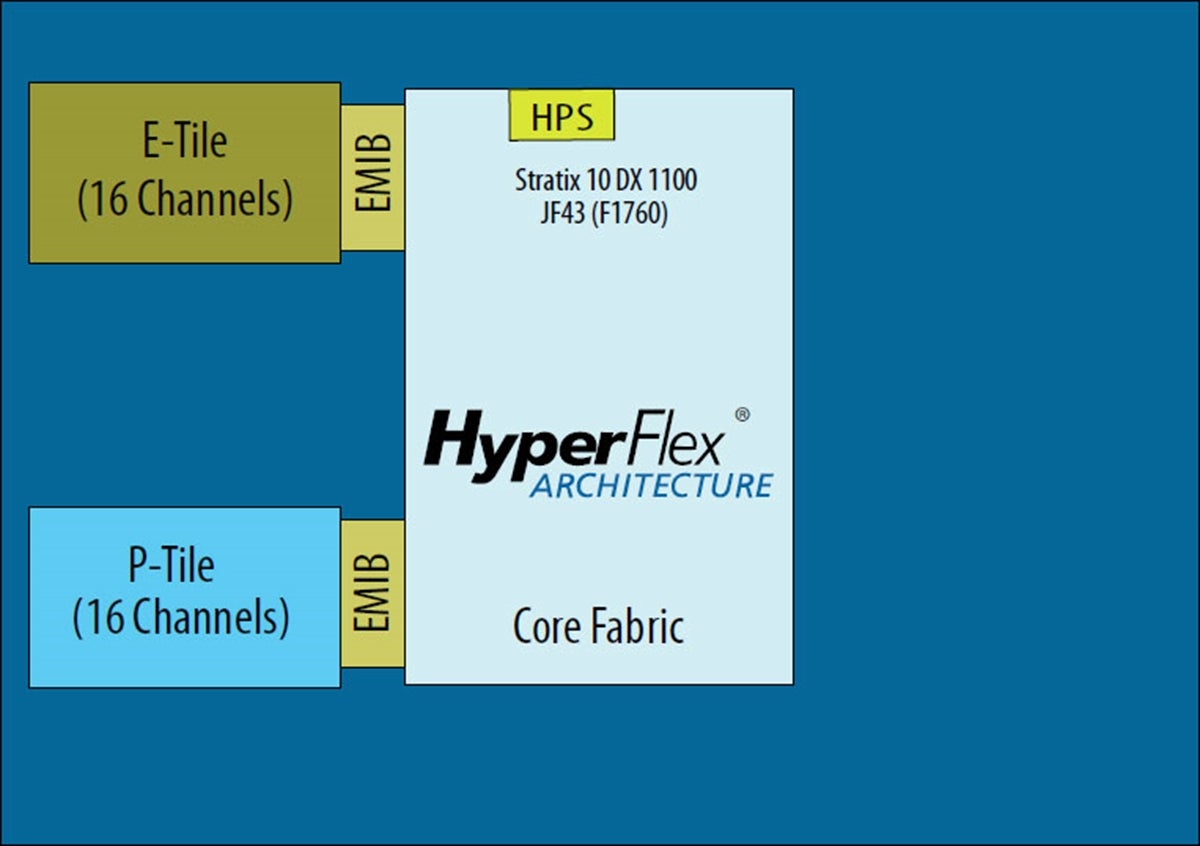

さて、DX 1100は一番シンプル(Photo07)で、E-TileとP-Tileが1つずつ、HBM2も存在しない(Photo08)。

HBM2を搭載するのがミドルレンジのDX 2100で、P-Tile×3+E-Tile×1、さらに合計8GBのHBM2メモリを搭載する、Photo07と一番近い構成である(Photo09)。

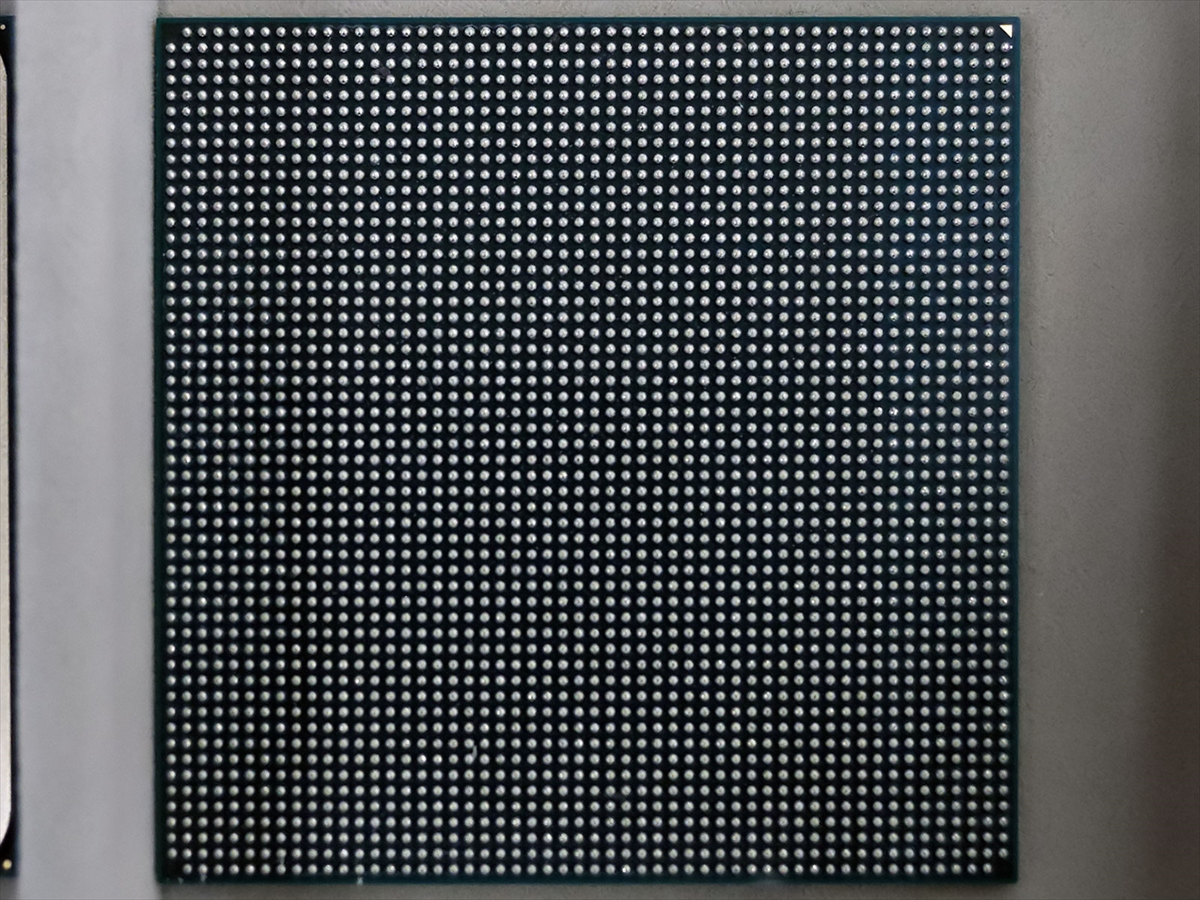

そしてハイエンドのDX 2800はHBM2無しの代わりにP-Tile×4+E-Tile×1という構成になっている。説明会場ではこのDX 2800のサンプルも展示された(Photo11~13)。

このP-Tileについてちょっと余談を1つ。説明の中でDorsey氏は「現時点ではPCIe Gen4のComplianceを取得した唯一のFPGAである」とした。実際確認してみると、確かにXilinxその他のFPGAはPCIe 4.0のCompliance Program Listに載っておらず、今のところStratix 10 DXが唯一のFPGAであることは間違いない。それはともかくとして、リストを見てみると"P-Tile for Intel Stratix 10 DX and Agilex FPGAs"という書き方になっている。つまりStratix 10 DXと(少なくとも第一世代の)AgilexのP-Tileは共通のものが利用される事になるようだ。

このStratix 10 DX、現状はサンプル出荷が開始という段階であるが、量産開始は2019年12月を予定している。またプラットフォーム(この中にはPACカードも含まれることになるだろう)は2020年中にリリース予定、との話であった。