VLSIシンポジウム 2024における回路部門(以前のVLSI Circuits Symposium)について、VLSIシンポジウム委員会では合計11件の注目論文を事前公開している。今回はその中から、プロセッサ分野、アクセラレータ分野、メモリ回路アーキテクチャ分野の3件の注目論文を紹介したい。

プロセッサ/SoC分野の注目論文

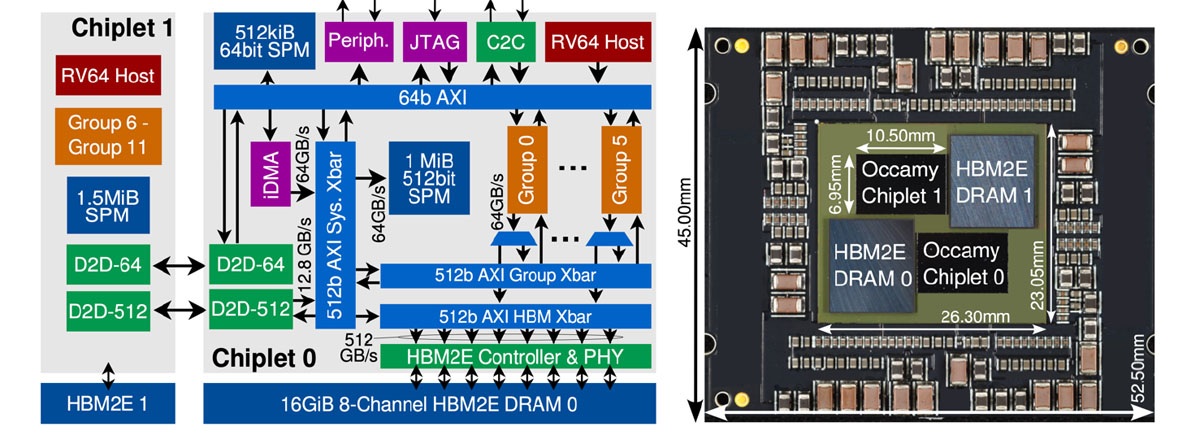

12nm FinFETで実装したチップレット採用の432コアRISC-Vベースアクセラレータをチューリッヒ工科大などが開発

- Occamy: A 432-Core 28.1 DP-GFLOP/s/W 83% FPU Utilization Dual-Chiplet, Dual-HBM2E RISC-V-based Accelerator for Stencil and Sparse Linear Algebra Computations with 8-to-64-bit Floating-Point Support in 12nm FinFET(論文番号:C7-4)

物理計算やグラフ解析分野におけるスパースデータ処理では、不規則なメモリアクセス・間接参照演算により演算器の使用効率が低下してしまうため、処理柔軟性を維持しつつ使用効率を高める手法が求められている。

この課題の解決に向けて、スイスのチューリッヒ工科大学、米スタンフォード大学、伊ボローニャ大学の共同研究グループは、汎用かつ柔軟なデュアルチップレットシステムを提案する。

このOccamyというコードネームのヘテロジニアスシステムは、広範囲の不規則なメモリアクセスを伴う計算ワークロードを高い演算器使用率で対応するために最適化された2つの16GB HBM2Eスタックを備えており、64ビット浮動小数点ならびに狭ビット幅(32-、16-、8ビット)SIMD型浮動小数点データによる効率的なスパース線形代数演算およびステンシル演算のために432コアRISC-V・デュアルチップレット2.5Dシステムで構成されている。

カスタム拡張されたRISC-Vコアで構成された48個のクラスタ、2つの64ビットホストコアおよびレイテンシ耐性を持つマルチチップレット間接続と32GB HBM2Eメモリシステムという特徴があり、実チップにてステンシル演算(83%)、疎行列-密行列乗算(42%)および密行列-密行列乗算(49%)という使用率を達成したとする。

機械学習のためのデバイスとアクセラレータ分野の注目論文

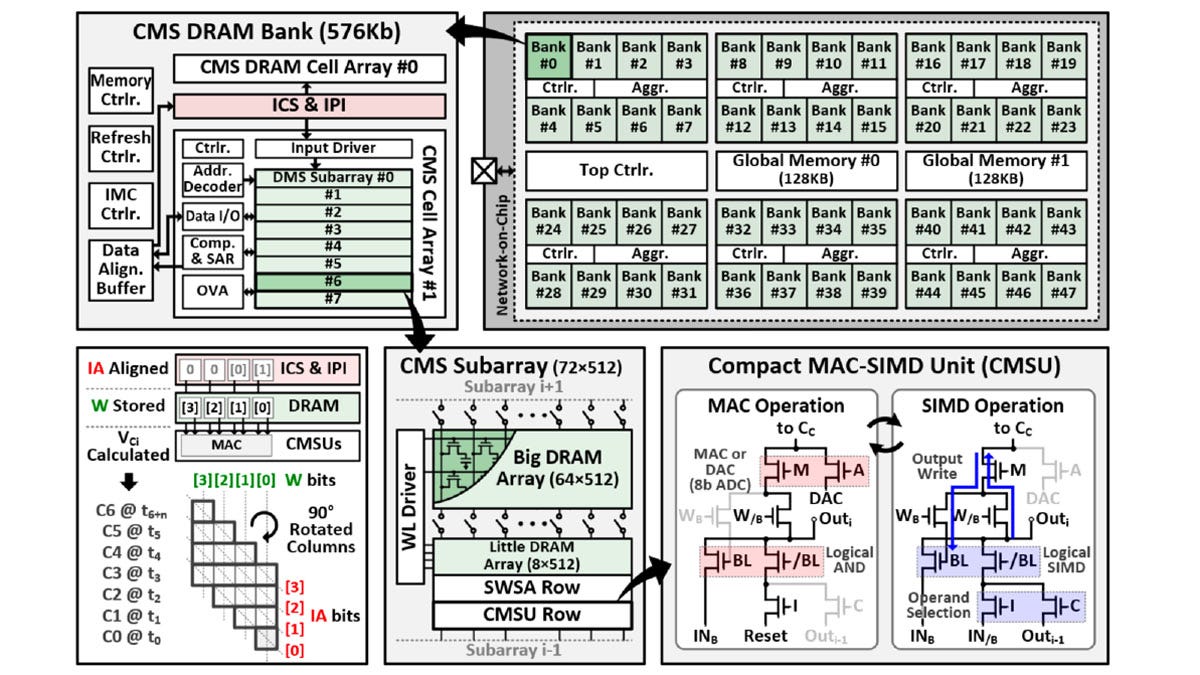

コンパクトなMAC-SIMDと適応型列加算データフローを備えた1T1C型DRAMインメモリコンピューティングアクセラレータをKAISTなどが発表

- Dyamond: A 1T1C DRAM In-memory Computing Accelerator with Compact MAC-SIMD and Adaptive Column Addition Dataflow(論文番号:C20-1)

1T1C型DRAMを用いたインメモリアクセラレータでは、計算回路が大きいためにメモリ密度が限定されることとSQNRを保ってエネルギー効率を上げるのが難しいという課題があった。

そこで、韓KAIST(Korea Advanced Institute of Science and Technology)とSamsung Electronicsの共同研究グループは、メモリアクセスを削減することでシステムのエネルギー効率を高め、メモリ密度を向上させる1T1C型DRAMインメモリコンピューティングアクセラレータを提案する。

コードネーム「Dyamond」と名付けられたアクセラレータは、高密度とエネルギー効率を実現する列加算(CA)データフローを備えており、それを活用したLSB-CAはA/Dコンバータ(ADC)の読み出しを最小限に抑え、エネルギー効率を高めることを可能とした。また、信号強化多重累積(MAC)および信号シフトADCを備えたMSB-CAは、SQNRを向上させてエネルギー効率をさらに向上させたとする。さらに、切り替え可能なセンスアンプにより、低電力インメモリ演算SIMDの読み取りエネルギーを低減している。

なおDyamondは、28nm CMOSプロセスで製造され、6.48mm2のダイ面積に27MビットDRAMメモリを集積し、27.2TOPS/Wのピークエネルギー効率と、機械学習モデル(ResNet、BERT、GPT-2)で優れたパフォーマンスを発揮したという。

メモリ回路アーキテクチャ部門の注目論文

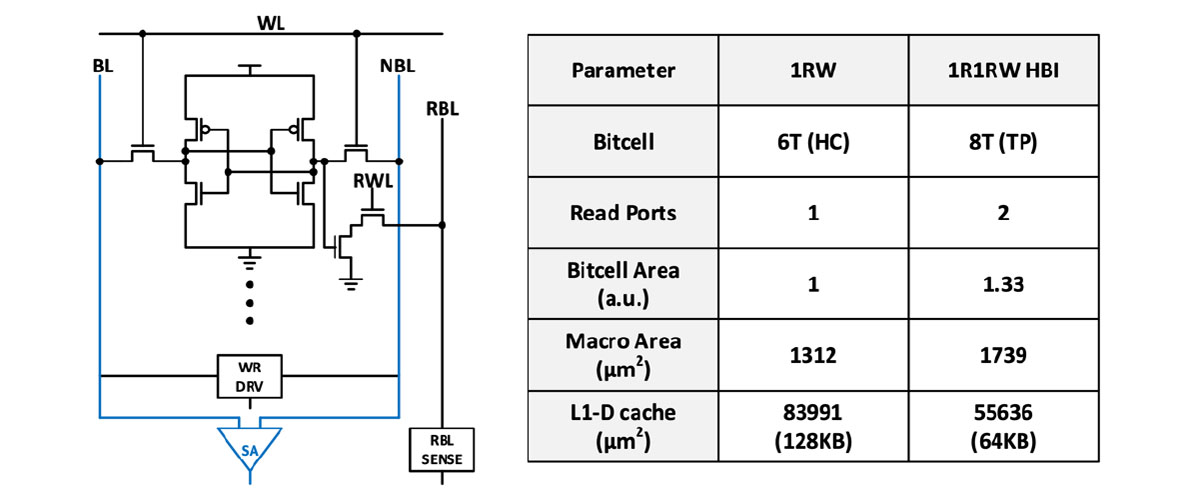

3nmプロセスHPCプロセッサ向け7GHz高バンド幅1R-1RW SRAMをArmが発表

- A 7GHz High-Bandwidth 1R-1RW SRAM for Arm HPC Processor in 3nm Technology(論文番号:C16-3)

CPUの性能向上に重要なSRAMのスケーリングペースは鈍化しつつあり、プロセスの進歩のみにSRAMの性能向上を求めるのは困難となっている。

そうした背景を踏まえ、Armは自社の高性能プロセッサに統合可能な3nm CMOSプロセス向けの1リード-1リードライト型(1R1RW)の高バンド幅インスタンス(HBI)メモリを発表する。

同メモリ技術は従来の8トランジスタを使用する1リード-1ライト型(1R1W)メモリを拡張し、追加の読み取りポートを備えることで、1R1RW機能を実現したという。これによりL1データキャッシュの利用可能な読み取り帯域幅を倍増させ、サイクルあたりの命令実行数は1%超改善したとする。さらに、HBIメモリの新規アーキテクチャにより、CPUの物理設計における配線混雑を緩和することでデータキャッシュ面積を13%減少し、配線遅延を10-15psec短縮したとする。

テストチップの評価から、1R1RW HBIメモリの歩留まりは100%であることを確認したほか、これまでに報告された8トランジスタSRAMメモリの中でも最高クラスとなる7GHz以上の動作周波数と11.2Mbit/mm2のビット密度を実証したとしている。