VLSIシンポジウム 2024における回路部門(以前のVLSI Circuits Symposium)について、VLSIシンポジウム委員会では合計11件の注目論文を事前公開している。今回はその中から、デジタル回路、医用生体回路、データコンバータ回路分野の3件の注目論文を紹介したい。

デジタル回路分野の注目論文

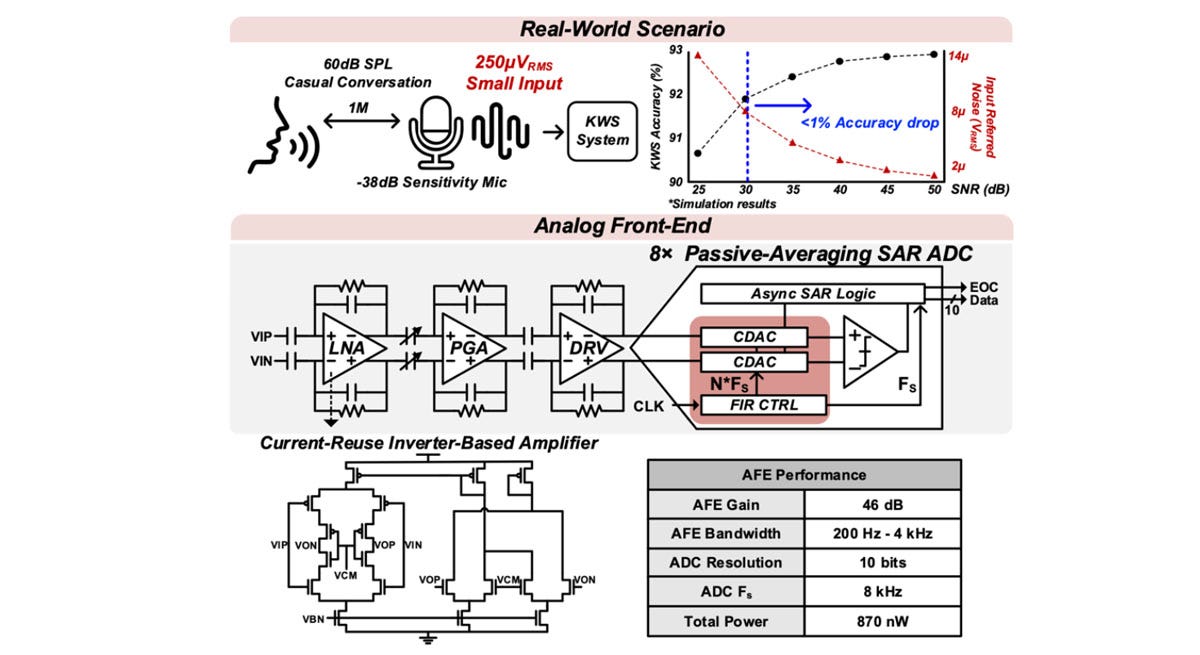

受動平均化SAR ADCと符合・指数のみのレイヤフュージョンを利用した音声認識システムをソウル大などが発表

- A 5.6μW 10-Keyword End-to-End Keyword Spotting System Using Passive-Averaging SAR ADCand Sign-Exponent-Only Layer Fusion with 92.7% Accuracy(論文番号:C25-1)

モバイルやIoT機器の起動や制御のための音声認識システムは、常時ON状態で入力を受け付ける必要があるため、低消費電力化が強く求められる分野であるが、従来手法ではキーワード数が増えると精度と低電力の両立が課題となっていた。

そうした状況を踏まえ、韓国のソウル大学と米コロンビア大学の研究チームは、モバイルおよびIoT機器の起動や制御に利用するEnd-to-Endの10キーワード音声認識システムを発表する。

提案されるアーキテクチャでは、受動平均化処理を採用することで、アナログフロントエンド(AFE)回路の信号対雑音比(SNR)を改善。それに伴い、消費電力のオーバーヘッドも20nWに抑えて動作できるようになったとするほか、符号・指数のモノレイヤフュージョン方式により、キーワード認識の精度を維持しながら、認識モデルの規模を63.5%、乗算に必要な消費電力を29.8%削減することに成功しており、10キーワード音声認識システムとして、92.7%の認識精度を5.6μWの消費電力で達成したという。

医用生体回路分野の注目論文

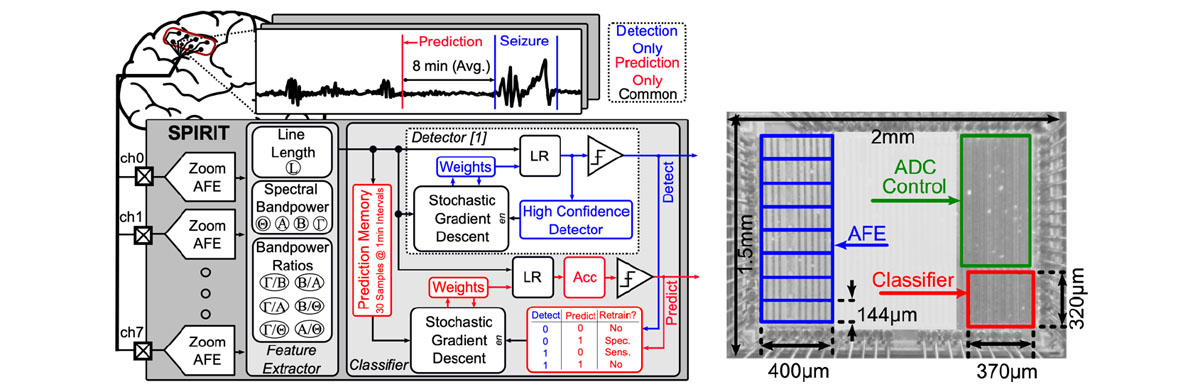

7SPIRIT: 17.2nJ/分類の教師無し逐次型学習による分類器とズーム型アナログフロントエンドを有するてんかん発作予測用SoCをカリフォルニア大が発表

- SPIRIT: A Seizure Prediction SoC with a 17.2nJ/clsUnsupervised Online-Learning Classifier and Zoom Analog Frontends(論文番号:C23-1)

てんかん発作の予測分類用SoCでは、これまで個人差に対応するためのモデル再学習に外部からの介入や作業が必要となっていた。

そうした現状を踏まえ、カリフォルニア大学バークレー校の研究チームは、「SPIRIT」と名付けた教師なし逐次型学習によるてんかん発作の予測分類器を集積したSoCを発表する。

このSoCは消費電力14.4μW、面積0.057mm2、ダイナミックレンジ90.5dBのズーム式AFEを8つ搭載することを特徴としており、平均して97.5%/96.2%の感度/特異度を達成、てんかん発作が起こる8.4分前に発作の予測が可能だという。また、この予測分類器全体の消費電力は17.2μW、占有面積は0.14mm2であり、これまでに報告された予測分類器の最小値と比較して電力を1/134、面積を1/5に削減したという。

データコンバータ分野の注目論文

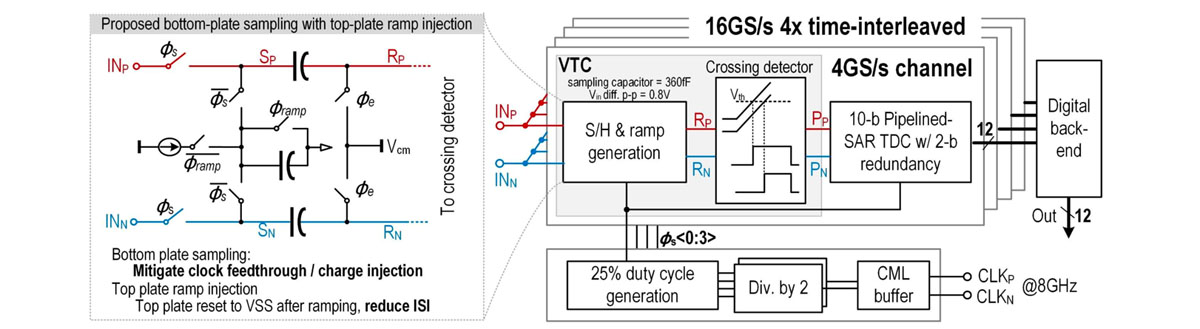

4nm CMOSプロセス採用のパイプライン逐次比較型TDCを用いた16GS/s、10ビット時間領域ADCを南カリフォルニア大などが発表

- A 16GS/s 10b Time-domain ADC using Pipelined-SAR TDC with Delay Variability Compensation and Background Calibration Achieving 153.8-dB FoMin 4nm CMOS(論文番号:C24-2)

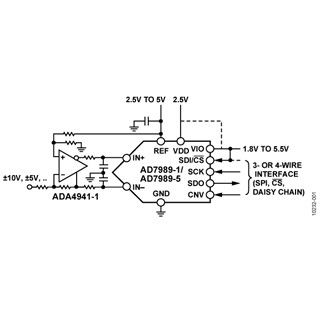

各種の高速無線・有線通信技術において高サンプリングレートのA/Dコンバータ(ADC)が必要不可欠であり、中でも時間領域ADC技術は、先端CMOSにおいて高速・高効率を両立できる可能性の高い技術として注目されている。

南カリフォルニア大学とMediaTekの共同研究グループは、4nm CMOSプロセスを用いた4チャネルタイムインターリーブ型10bit、16GS/sのダイレクトRFサンプリング時間領域ADCを提案する。

このアーキテクチャは、冗長性による時間-デジタル変換回路の遅延ばらつき補正手法、遅延オフセットのバックグラウンドでの補正手法、そしてボトムプレートサンプリングを用いた電圧-時間変換回路(VTC)構造を用いて、高い信号対雑音比(SNR)と線形性を達成するというもので、試作されたチップでは8000μm2のアクティブ面積で実装され、ナイキスト入力周波数において55.93dBのSFDRと44.48dBのSNDRを94.2mWの消費電力で達成したとするほか、Schreier FoMでは153.8 dBという性能を達成したという。