分数次数インピーダンス

このセクションでは、分数次数インピーダンスを近似する方法を説明します。これにより、コントローラの誤差アンプの周波数特性を定義できます。

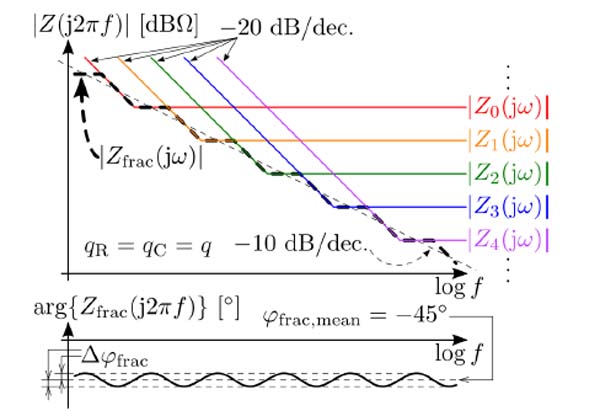

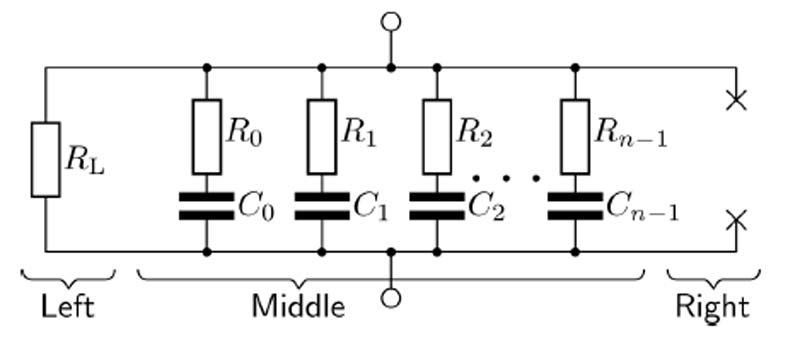

ゲインZFが正で、分数次数αが0~1の間にあるインピーダンスZ(s) = ZFs-αは、図4に示す無限RCラダーで近似できます[9][10]。

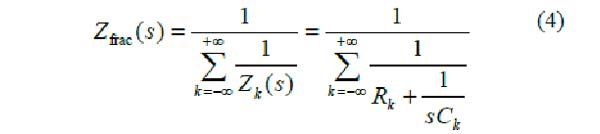

無限RCラダーのインピーダンスは参考文献[9]で説明されています。

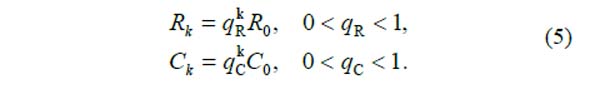

ここで、Zk(s)はk番目の系列に相当するRC回路のインピーダンスです。抵抗Rkと静電容量Ckは、徐々に減少する個別の幾何系列を形成します[9][10]。

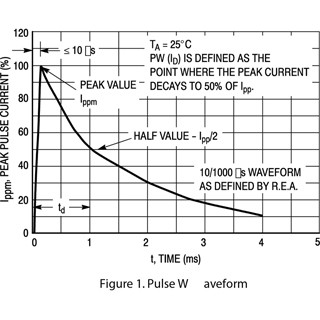

無限RCラダーの動作を図5で説明します。共通の比であるqRとqCが同一(qR = qC = q)と仮定します。k番目の系列に相当するRC回路のカットオフ周波数は(1/qk)2に比例し、この周波数におけるRC回路のインピーダンスは1/qkに比例します[9]。その結果、無限RCラダーのインピーダンスZfrac(s)の大きさは、勾配の平均値の半分、つまり–10dB/decに従います。

インピーダンスZfrac(s)の周波数特性のうち位相は、近似するインピーダンスZFs-αの位相φfrac,meanの周辺で、Δφfracの大きさのリップルで発振します。同様なことが振幅にも当てはまります。共通の比であるqRとqCを選択する際に、1に近い値を使用するとリップルを低減できます。比qC/qRは、近似しようとするインピーダンスの次数αを設定します。

参考文献[9]の図5に示すように、特定の周波数に近いカットオフ周波数を持つ系列のRC回路のみが、この周波数での分数次数の挙動に寄与します。

無限RCラダーを実際に実現することはできませんが、以下の3つのセクションに分割することは可能です。中間セクションは、対象となる周波数帯における分数次数インピーダンスを近似するのに対し、左と右の各セクションは、RCラダーを「終端」します。これにより、無限RCラダーは、図6に示すように、両端を終端した有限RCラダーに縮小することができます。

左側のセクションは、左端の終端抵抗RLで近似しており、1つの幾何系列を評価する方法で求めることができます[9](左側のセクションは、対象の周波数で主に抵抗性の挙動を示すことを想定)。

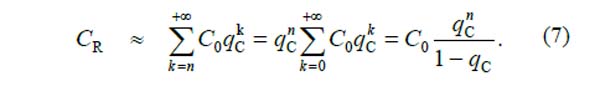

同様に、右側のセクションは、主に容量性の挙動を示すことを想定しており、右側の終端静電容量で近似します。

終端抵抗と終端静電容量を除外して考えると、両端を終端したRCラダーが、許容可能な分数次数の挙動を示す周波数帯は狭くなります[9]。「終端」という用語は、伝送ラインの終端に似た比喩的表現です(伝送ラインの周波数応答を安定させることが目的)。両端を終端した有限RCラダーは、図7の特性(b)が示す周波数特性を達成します。

ここでは、両端を終端した有限RCラダーの代わりに、図8に示す左側を終端した有限RCラダーを使用します。右側の終端静電容量CRの役割は、LDOの寄生極によって満たされ、レギュレーション・ループで追加の位相マージンを確保できます。寄生極が存在しない場合、左側を終端したRCラダーは図7に示す周波数特性(c)を達成します。

参考文献[9]のセクション5は、RCラダーが、個別の(マッチングしていない)素子による変動の影響をあまり受けないことを示しています。複数の変動が同時に発生する場合(プロセス拡散)でも、インピーダンスのスケール化のみ発生し、次数αに影響を及ぼしません。

(次回は10月19日の掲載予定です)

参考文献

[9] VALSA, J., DVORAK, P., FRIEDL, M. Network Model of the CPE. Radioengineering, 2011, vol. 20, no. 3, p. 619–626. ISSN 1805-9600.

[10] PETRŽELA, J. Phase Shifters Using Passive Realizations of Fractal Capacitors (Posouvač fáze založené na využití pasivních realizací fraktálních kapacitorů). Slaboproudý obzor, 2014, no. 2, p. 6–12. ISSN 2336-5773.

著者プロフィール

Pavel Horský (パヴェル・ホルスキー)オン・セミコンダクターの技術スタッフのメンバーで、専門分野はEMC、ESD、信頼性を重視した自動車用アナログ/ミクスド・シグナルIC設計。

1997年から、アルカテル・マイクロエレクトロニクス、AMIセミコンダクター、オン・セミコンダクターで、アナログおよびミクスドシグナル・デザインエンジニア、テクニカル・プロジェクト・リーダー、アナログASIC設計グループのリーダーを歴任。

チェコ共和国ブルノ工科大学で、1994年にラジオエレクトロニクス理学士号、1998年に計測学で博士号を取得。

2011年から同大学准教授として、博士課程の学生向けにアナログデザインコースを担当。60の出版物の著者および共同著者、15の米国特許の起草および共同起草者。

Libor Kadlčík (リボル・カドルーク)

オン・セミコンダクターのチェコ共和国にあるデザインセンターで、アナログASIC設計グループに所属。

チェコ共和国のブルノ工科大学で、2011年に電子通信学の理学士号、また2013年に理学修士号を取得。

現在、同大学の電子通信技術(D-EST)プログラムの博士号を取得中。