寄生成分の少ないクリーンなMOSFETスイッチング

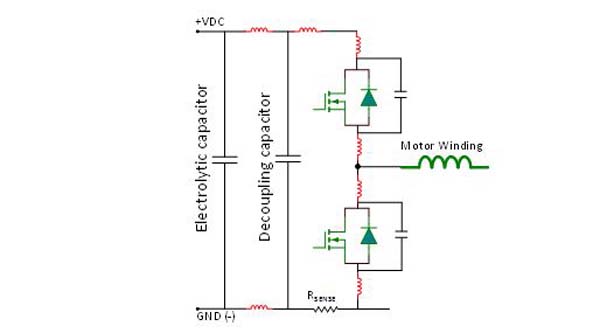

図2は、電力段PCB設計での部品のリードや最適化されていないレイアウトに起因する寄生インダクタンスと寄生容量を示しています。これらのPCB寄生成分が電圧リンギングを発生させ、結果としてMOSFETに電圧ストレスがかかります。

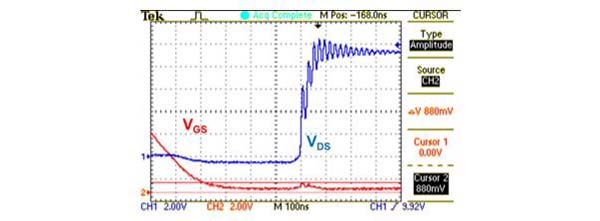

リンギングの原因の1つはダイオードの逆方向回復です。高速スイッチングに起因する高い電流変化率により、ダイオードの逆方向回復電流が増大することがあります。逆方向回復電流は、レイアウトの寄生インダクタンスを介して流れます。FET容量と寄生インダクタンスによって形成される共振回路が位相ノードのリンギングを引き起こし、それによって電圧マージンが減少してデバイスに対するストレスが増大します。図3は、回路寄生成分が引き起こすディスクリートMOSFETでの位相ノード電圧リンギングを示しています。

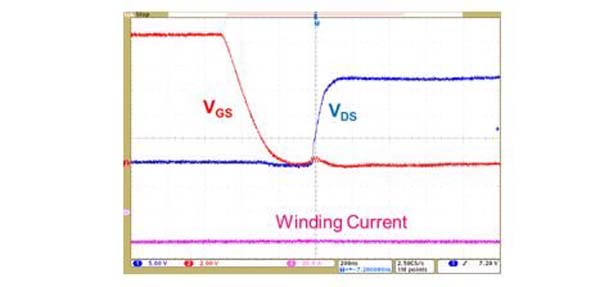

パワー・ブロックを使用した場合は、2つのMOSFETを接続するスイッチ・ノード・クリップによってハイサイドおよびローサイドMOSFET間の寄生インダクタンスが絶対最小値に維持されます。ローサイドFETとハイサイドFETを同じパッケージ内で使用することによってPCB寄生成分が最小限になり、位相ノード電圧リンギングが低減します。

これらのパワー・ブロックを活用すれば、図4に示すように、50Aに及ぶ大電流が流れた場合でも電圧オーバーシュートを発生させることのない、スムーズなMOSFETスイッチングが実現できます。

PCB寄生抵抗の低減による低PCB損失の実現

パワー・ブロックは、大電流が流れるPCB上のパターンを短くするのに役立つため、パターンでの電力損失の低減につながります。

ディスクリートFETを使用した場合のPCBパターン要件について理解していきましょう。

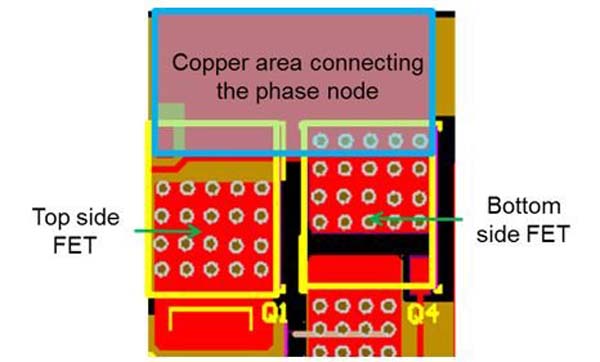

上側および下側ディスクリートMOSFET間のPCBパターン接続により、PCB上でI2Rの損失が発生します。図5は、上側および下側ディスクリートMOSFETを横並びに接続した場合の銅パターンを表しており、PCBに対してモーター巻線を簡単に接続するための一般的なレイアウトの1つです。

位相ノードに接続されている銅領域の長さは、その幅の2倍あります(パターン幅は電流に応じて決まり、通常は基板のフォーム・ファクタによって制限されます)。また、上側および下側ディスクリートMOSFETを、間に位相ノードを挟んで上下に配置することもできます。ただし、モーター巻線を位相ノードに接続するための対策が必要になるため、パターン長を短縮できない可能性があるほか、そのような配置がすべてのアプリケーションに適しているとも限りません。

設計に厚さが2オンス(70μm)のPCB銅領域がある場合、図5に示す、位相ノードを接続している単層PCBパターンは、抵抗値が約0.24mΩとなります。2つのPCBプレーンにパターンが存在すると仮定した場合、等価PCB抵抗は0.12mΩです。3相電力段の場合は、そのようなPCBパターンが3つあります。同じような分析を、DC電源の入力とリターンの各パターンに対して行うこともできます。

単一のパッケージに上側および下側MOSFETを備え、パッケージ内部の金属クリップによって位相ノードが接続されているパワー・ブロックは、寄生抵抗を最適化し、レイアウトの柔軟性を実現し、総PCB抵抗を最小0.5~1mΩに削減します。

(次回は10月18日に掲載します)

著者プロフィール

マヌ・バラクリシュナン (Manu Balakrishnan)テキサス・インスツルメンツ

産業用モーター・ドライバ事業 システムエンジニア