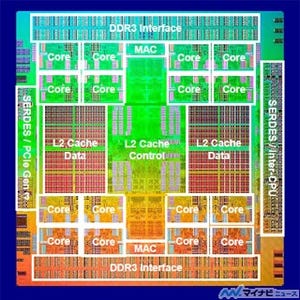

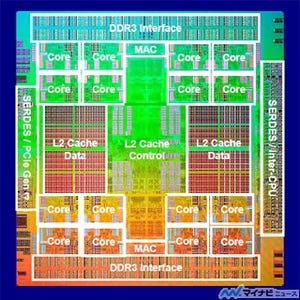

M6プロセサの構成

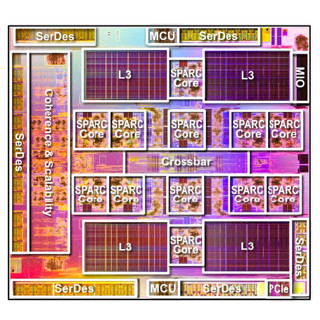

M6プロセサのブロック図は次のようになっている。

12個のS3コアと4つの12MBのL3キャッシュが12×5のクロスバで接続され、また、IO subsystemもS3コア群と繋がっている。そして、2個のコヒーレンスユニットを経由して2個のメモリコントローラと、図の右側に書かれた7つのC-Linkポートと、図の左に書かれた6つのS-Linkポートに繋がっている。

メモリサブシステムは、2個のコントローラの中にそれぞれ2つのスケジューラがあり、各スケジューラから2個のBoBと呼ぶチップを経由してDIMMに接続している。1個のBoBチップに4枚のDIMMが接続できるので、全体では32DIMMで、32GB DIMMを使えば、1TBのメモリ容量となる。

大型サーバの用途として、巨大メモリにすべてのデータを載せて、高速にデータベース処理を行うインメモリデータベースが流行っており、SPARC M6のメモリサブシステムは、インメモリデータベースを効率よく実行するようにチューニングされているという。

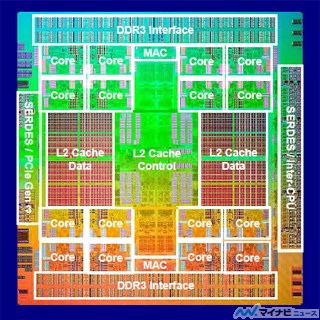

8チップ1グループで、それをさらにグループ化して大規模システムを構築

SPARC M6プロセサは7ポートのC-Linkを持っている。このポートで8チップの間を完全結合したグループを作り、それらをS-Link経由でBixbyと呼ぶチップに接続して、複数のグループ間を繋いでいる。

S-Linkは16Gbpsのx8リンクで、各方向16GB/sの伝送速度を持つリンクとなっている。

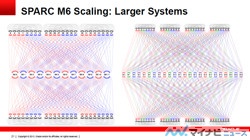

この図は32ソケットのシステムの構成図で、4つの8チップグループを12個のBixbyチップで接続している。この構成では、1つのBixbyチップと8チップグループの間は4本のS-Linkで接続されており、Bixbyチップは、4つすべての8チップグループと接続されている。実は、Bixbyチップは24本のS-Linkを扱えるのであるが、この構成では16本しか使用されていない。

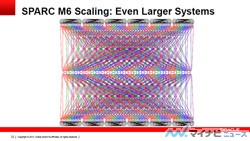

48ソケット、そして64ソケットのシステムの構成は次の図のようになる。

48ソケットの場合はBixbyチップの24本のS-Linkをフルに使い、6つの8チップグループに各4本のS-Linkで接続している。また、64ソケットシステムでは、24個のBixbyチップで8個の8チップグループを接続しているが、接続はS-Link2本ずつとなっており、この場合も16本のリンクしか使われていない。これを24本のS-Linkをフルに使うと12個の8チップグループが接続でき、最大構成の96ソケットのシステムとなる。

8チップのグループからは24ペアのS-Linkが出ているが、それぞれのリンクは異なるアドレス空間を分担しており、他のグループのプロセサのメモをアクセスする場合は、まず、C-Linkを使って、目的のアドレスを担当しているプロセサに要求を送り、そのプロセサから、アクセスするアドレスのメモリを管理するBixbyチップの1つに要求を送るという手順になる。

Bixbyチップは、データの通路となるクロスバと、ディレクトリから構成されており、システム内のデータ転送とキャッシュコヒーレンシの制御を行う。メモリアクセスの要求元のプロセサは、Bixbyチップのディレクトリにアクセス要求を送り、同時に、そのアドレスのメモリを持つプロセサ(メモリホーム)に投機的読み出し要求を発行する。そして、ディレクトリはアクセスされたラインの状態をチェックし、要求受付を返す。

アクセスされたラインがどのプロセサのキャッシュにも入っていない場合は、メモリホームに対して投機的読み出しの結果を、要求元に送るように指示する。一方、アクセスされたラインがどこかのプロセサのキャッシュに入っている場合は、ディレクトリは、データを持っている1つのプロセサにキャッシュの内容を要求元に送るように指示し、その他の同じデータを持っているプロセサにはそのキャッシュラインを無効化する指示を送る。

そして、要求元は、無効化受け入れ応答が揃うと、ディレクトリに完了を通知して、そのラインへのアクセスを可能にするというようになる。