4年ぶりのHot Chipsでの発表となったPOWER製品「POWER8」

今回のHot Chips 25で、IBMはPOWER8を発表した。POWER7の発表はHot Chips 21であるので、実に4年ぶりのHot Chipsでの発表となる。

製品としては、45nmプロセスのPOWER7を32nmプロセスにシュリンクしたPOWER7+があるが、このチップはHot Chipsでは発表されていない。

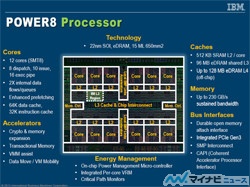

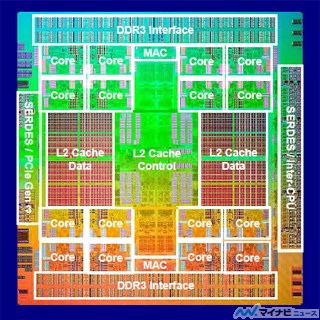

この図に見られるように、POER8は22nm SOIプロセスを使い、8スレッドを並列に実行するコアを12個集積したチップである。そして、コアごとに付属しているL2キャッシュが合計6MB、共通のL3キャッシュが96MB、さらに、別チップで128MBのL4キャッシュが付くというキャッシュの塊りのようなプロセサである。

22nmプロセスながら650平方mmという巨大なチップサイズ

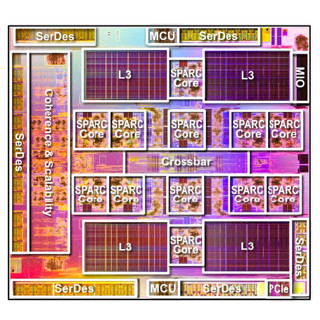

22nm SOIプロセスを使い、15層の配線を使っているにも拘わらず、チップサイズは650平方mmとなっている。富士通のSPARC64 X+やOracleのSPARC M6は28nmバルクプロセスを使っており、POWER8を28nmプロセスで作れば1000平方mmを超える計算になる。富士通やOracleのプロセサチップは600平方mm程度であり、POWER8の巨大さは際立っている。

プロセサコアは8命令発行で、10命令イシュー、16本の実行パイプラインと書かれている。これまでのプロセサはOut-of-Order実行を行うものでも4命令発行程度であり、8命令というのは例が無い。1つのスレッドから8命令を発行できる機会は少ないので、複数スレッドの合計で8命令ではないかと思われるが、それにしても強力なコアである。

また、POWER7と比較すると、L1データキャッシュの容量を2倍の64KBに増やし、TLBのサイズを4倍にし、L2キャッシュからL1キャッシュへのバス幅を2倍にするなど、メモリアクセス側も強化されている。

結果として、POWER7コアと比較して、シングルスレッドでの性能は1.6倍、最大スレッド数でのスループット性能は2倍に向上しているという。

このチップ写真からコアの面積を推定すると、約16平方mmとなる。一方、富士通のSPARC64 X+のコアは10.8平方mm程度であり、22nmと28nmのプロセスの違いを考慮すると、POWER8のコアは約2.4倍の面積である。この点からもPOWER8コアは巨大なモンスターコアである。

このスライドで、もう1つ、注目されるのが、Integrated Per-core VRMという記述である。素直に読むと、POWER8の12個のコアごとに、集積化された電圧安定化モジュール(Voltage Regulator Module)があるということになる。

IntelのHaswellが、CPUチップに集積したVRMを持ち、6系統の電源を供給すると発表されているが、コアの電源電圧は1系統で、コアごとに電源電圧を変えることはできない。このため、負荷が低く、低い電源電圧で遅めのクロックでも良いプロセサコアにも高い電源電圧が供給され、ムダに大きなエネルギーを消費してしまう。

コアごとに電源電圧を変えることが出来れば、各コアの動作状態に応じてクロックと電源電圧を最適値に設定できる。つまり、POWER8のコアごとの安定化電源というのは動作エネルギー削減の究極の形を実現したことになる。

12個のコアに加えて、L3キャッシュとかメモリコントローラの電源も必要であり、必要なVRMの数は14かそれ以上になると思われる。そして、VRMごとにコイルとコンデンサが必要になり、これらをどのように集積しているかが興味のもたれるところである。

ということで、AMDのSam Naffziger氏と筆者が質問をしたのであるが、発表者のStuecheli氏は、ネストアーキテクト(IBMではコア以外の部分をネストと呼ぶそうである)で、VRMの話はまったく知らないということで、何も聞き出すことができなかった。また、これだけの数のVRMとなると、相当の面積を必要とすると思われるが、チップ写真にもVRMと表示された部分は存在せず、どのように実現されているのか謎である。