低消費電力技術やチップ間通信のエラー対策など、細かな部分まで配慮

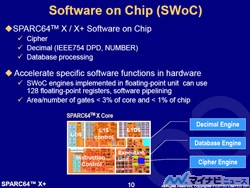

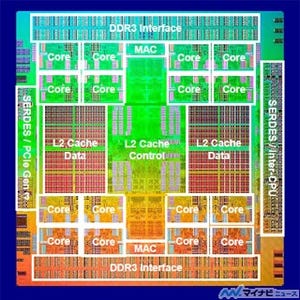

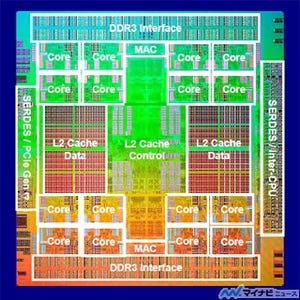

この図に見られるように、SWoCとしてチップに追加したハードウェアはわずかでプロセサコアの面積増加は3%に満たないという。

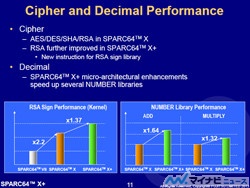

SPARC64 X+では命令の追加や回路の改良で、SPARC64 Xと比較して、RSA暗号を使った署名の計算カーネルの処理性能は1.37倍、NUMBERの加算は1.64倍,乗算は1.32倍に性能を向上させている。

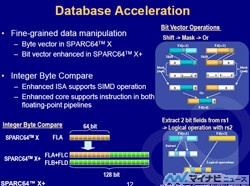

データベースの加速機構は、2つのレジスタの内容をそれぞれ異なる量のシフトを行い、それぞれにマスクをANDし、それらの結果をORでまとめるビットベクタ演算を行う。具体的にどのようなところで使われ、どの程度の性能向上効果があるのか分からないが、ソフトウェアで行うと面倒だが、ハードウェアでは簡単に実現できるので、効果的なエンハンスである。

このビットベクタ演算は、SPARC64 Xでは64bit同士のオペランドの演算を1個だけ実行していたが、SPARC64 X+ではベクタ長を128bitに伸ばし、かつ、1サイクルに2演算を実行できるように強化されている。また、右下に書かれたように、1つのオペランドから2つのビットフィールドを取り出してもう1つのオペランドと論理演算を行うという命令も追加されている。

RAS(Reliability、Availability、Serviceability)はハイエンドサーバでは重要な機能で、命令のリトライなど富士通のSPARC64プロセサは業界トップのRASを組み込んできたが、SPARC64 X/X+もその伝統を受け継いでいる。

これまでのSPARC64と同じく、1bitエラーが起こっても回復できるグリーンと1bitエラーが起きても動作に関係ない灰色のところがほとんどで、エラー検出はできるが回復できない黄色の部分は比較的狭いコントロール部だけになっている。

また、今回、チップ間の高速通信路はCRCで保護されており、エラーが検出された場合は再送でリカバリを行うことが明らかにされた。そして、再送でも回復できない固定故障の場合は、ダイナミックに故障レーンを外して動作を続けることができるという。

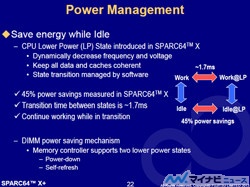

そして、SPARC64 Xから省電力機構が組み込まれたことが明らかにされた。デスクトップやモバイルのCPUに比べると、大型サーバプロセサの省電力化は遅れている感があるが、やっと富士通も腰をあげたという感じである。

低負荷の状態では、クロックと電源電圧を下げ、プロセサの消費電力を45%削減する。この低電力状態との切り替えには約1.7msかかるが、切り替えている間もプロセサは動作を続けられるという。

また、メモリコントローラもDRAMのPower-DownモードとSelf-Refreshモードという省電力状態にする機能をサポートしている。

このように、SPARC64 X+はミドルライフキッカーではあるが、クロック向上や各種のアーキテクチャ的改善を組み込んでおり、魅力のあるプロセサに仕上がっている。また、IntelのItaniumが怪しくなり、このクラスの大型サーバ用プロセサを開発しているところは、世界でも、IBM、Oracleと富士通だけになっており、富士通には引き続き頑張れとエールを送りたい。