2018年3月に概要が明らかにされ、同8月のHotChips 30で内部構造の一端が公開された「Project Everest」こと「ACAP(Adaptive Compute Acceleration Platform)」であるが、これの採用第1弾となる「Xilinx Versalシリーズ」がXDF 2018の基調講演で公開された。

この基調講演に先立って、このVersalシリーズの概要と、若干の詳細が明らかにされたので、まとめてご紹介したい(Photo01)。

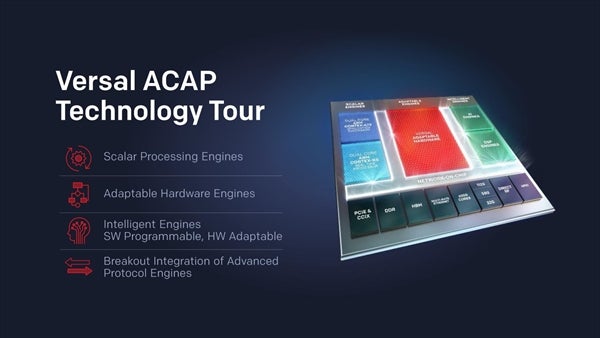

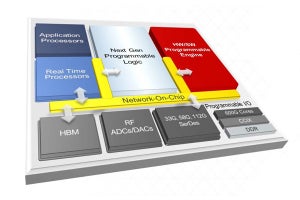

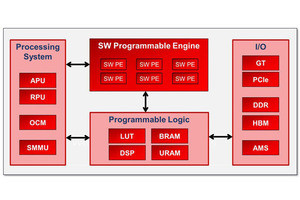

Versal、というかACAPはArmのプロセッサIP(Scalar Processing Engines)とFPGA Fabric(Adaptable Hardware Engine)、それに新しいS/W Programmable Engineと周辺回路から構成される(Photo02)というのは以前説明があった通り。

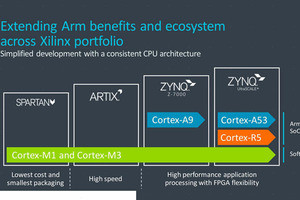

まずScalar Processing EngineはDual Cortex-A72とDual Cortex-R5構成となる(Photo03)。

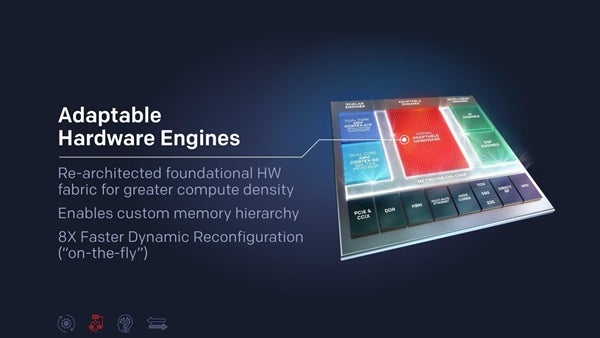

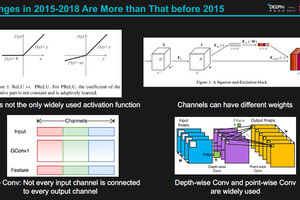

ついでFPGA Fabricだが、こちらは従来よりも高いロジック実度と、より柔軟なメモリ階層構造、それとDynamic Reconfigurationを従来比で8倍高速化した、とされる(Photo04)。

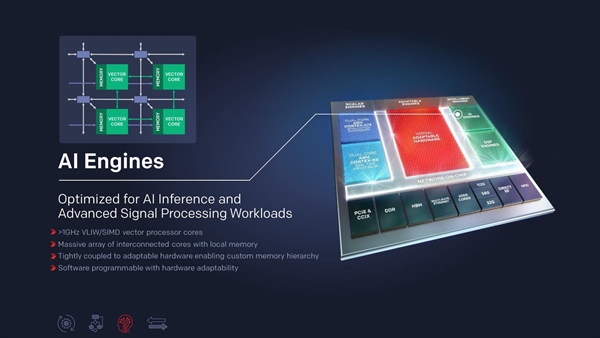

そしてIntelligence EngineとしてはAI EngineとDSP Engineが用意される(Photo05)。ちなみにAI Engineのほうの内部構造がこちら(Photo06)となっている。

-

Photo05:ここで出てきたML Vector Extentionsを搭載するのがAI Engines、5G Wireless Vector Extentisonsを搭載するのがDSP Engineということらしい。もっともDSP EngineはAI処理で利用することもあるようなので、このあたりが一対一対応していないのがまだ良くわからない部分である

Host I/FとしてはPCIe Gen4×16、AXI-DMA、それとCCIXをサポートする(Photo07)。またメモリはDDR4-3200とLPDDR4-4266、それと将来的にはHBM(HBM2と思われるが、時期的にはHVBM3の可能性もある)をサポートする(Photo08)。

-

Photo07:CCIXはPCIe Gen4のPHYとMACを利用しつつ、その上は独自という形で実装されるため、物理的にはPCIeのPHYということになる。ただ将来的には56GのPHYも利用可能なので、実はCCIXの実装はこれらのPHYの上にかぶさる形になるのかもしれない

Protocol Engineは100G Multirate Ethernetのほかに600GのEhernet/Interlakenがサポートされ、さらに600GのCryptographic Engineも搭載される(Photo09)。

また32/58/112Gのトランシーバが利用可能である(Photo10)。またこれも5Gの基地局向けに、Up/Down Conversionなしで直接利用できる高速ADC/DACやDDC/DUC、さらに5G/DOCSISに対応したFEC(Forward Error Collection)なども搭載されるとする(Photo11)。

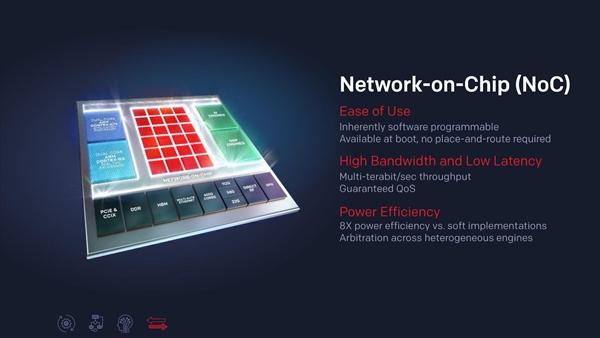

GPIO(Photo12)もMIPI D-PHYやNAND/SCM向けI/Fなどを搭載するなど、機能が充実している。最後がこうした各モジュールをつなぐネットワーク(Photo13)で、広帯域/低レイテンシと、従来のFPGAでアービトレーションを自分で行った場合と比較して8倍の電力効率を実現し、しかもプログラミングが容易とする。

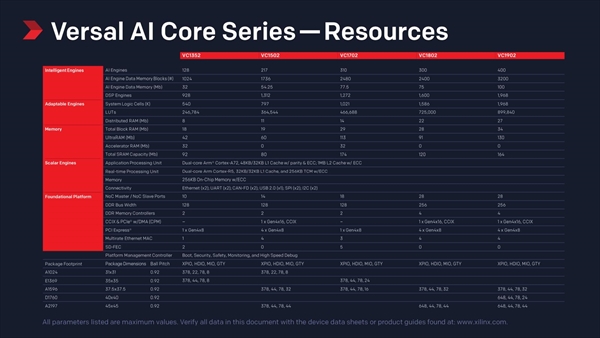

さて、こうした特長をもつVersalシリーズだが、第1世代はPhoto14に示す6種類の製品が用意される(Photo14)。ただ今回公開されるのはVersal AI CoreとVersal Primeの2つである。

まずPrimeシリーズはミッドレンジ向けというか、いわゆる一番汎用に近い構成で、AI Engineや112GのSerDes、HBMなどは搭載しない。具体的な用途としてはレーダーのビームフォーミング向けのIntelligent Engine、Network Attach Storage(NAS)、Network Attached Accelerator、さらには通信テスト機器/データセンターのネットワーク/ストレージ/100G Ethernet/Broadcast Switch/Medical Imaging/Avionics Controlなどが挙げられている。たとえばNetwork Attached Acceleratorのケースでは、Open vSwitchを実装する場合、CPU(4コアXeon)が8.68Mpackets/secなのに対し、Versal Primeで実装すると17倍の150Mpackets/secが可能になる、という数字が示された。

-

Photo15:Versalシリーズの中では事実上のローエンドであるが、これがミッドレンジということは、要するにVersalシリーズはローエンドにはそもそも入らない(最低でもミッドレンジ)という事だと思われる

一方のVersal AI Core(Photo16)の方はEdge AI Workloadに向けた構成となっており、たとえばGoogleNet V1の処理だとXeon比で43倍、GPU(Tesla V100)比で2倍の処理性能となっており、これが自動車などでの利用を前提に、レイテンシが7msとした場合はXeon比72倍、Tesla V100比で2.5倍に、さらにクリティカルなレイテンシ2msとするとTesla V100比で8倍の性能になるされる(2msの場合、CPUだと絶対に間に合わないそうだ)。また同じ消費電力(75W)にするとGPU比で4倍のスループットになる、とも説明されている。

ちなみにVersal AI Coreは、たとえば5Gのワイヤレスの処理にも向いており、CloudRANの制御とかSystolic Array/Baseband Processingに利用すると5倍の性能が、自己組織ネットワークの構築とかAnomaly Detection、スケジューリングなどに利用すると8倍の性能が得られるとし、ただし両立はしないのでどちらにどの程度性能を振るかを開発者が好きに調整できる、としている。

最後に製品ロードマップだが、今回発表のVersal AI CoreとVersal Primeは2019年後半に投入され、ついでVersal PrimeとVersal AI Edge/Versal AI RFが2020年中に、Versal HBMは2021年以降に投入されると説明された(Photo17)。

さらにVersal Prime(Photo18)とVersal AI Core(Photo19)の詳細な製品SKUも今回公開されている。

今回の事前説明ではTechnical Deep Diveは後日ということで、あまり突っ込んだ話はなかった。これらについては別にレポートする予定である。