Qualcommはスマートフォン用のプロセサではトップメーカーである。これまでのQualcommのプロセサはスマホ向けのSnapdragonだけであったが、Qualcomm Datacenter Technologies(QDT)という会社を作りデータセンター用のプロセサの開発を進めてきた。Qualcommは、その成果である「Centriq 2400」というプロセサをHot Chips 29において発表した。

|

|

Centriq 2400プロセサを発表するQDTのThomas Speier氏 |

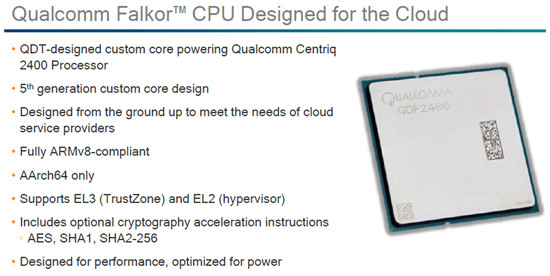

Centriq 2400プロセサに使われているプロセサコアは、Qualcommが開発した「Falkor」というコアである。Falkorはネバーエンディングストーリーに出てくる幸運をもたらす竜である。Snapdragonと言い、Falkorと言い、Qualcommは竜が好きである。

Falkorは第5世代のコアと書かれているが、これはスマートフォン用も含めてのプロセサ世代であると思われる。Falkorはクラウドサービス提供者のニーズに応えるよう、ゼロから設計されたとのことである。Falkorは、64bitアーキテクチャのARMプロセサである。ただし、32bitのARMアーキテクチャはサポートせず、AArch64だけのサポートとなっている。スマートフォンの場合は、これまでの32bitアーキのソフトを動かす必要もあるが、サーバ用のARMプロセサでは32bitのソフト資産は無いので、32bitアーキはサポートしなくても困らない。

|

|

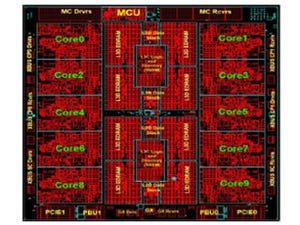

Centriq 2400のプロセサコアはFalkorと名付けられている。Falkorコアは、ARMの64bitアーキテクチャのプロセサであり、クラウドサービス提供者のニーズに応えるようにゼロから新規設計されている (このレポートの図は、Hot Chips 29におけるQualcommの発表資料のコピーである) |

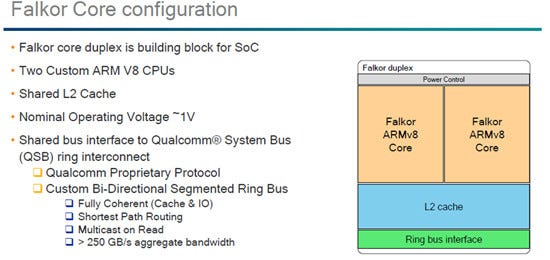

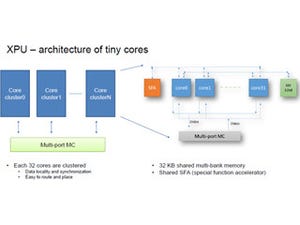

次の図に示すように、Falkorコアが2コアとL2キャッシュからなるFalkor Duplexが構成単位となっている。そして、Falkor DuplexはQualcomm System Bus(QSB)というリングバスのインタフェースを備えている。

QSBは双方向のセグメント化されたリングバスであり、総バンド幅は250GB/sを超える。Qualcomm独自のプロトコルを使い、キャッシュやI/Oとのコヒーレンシを維持するバスとなっている。

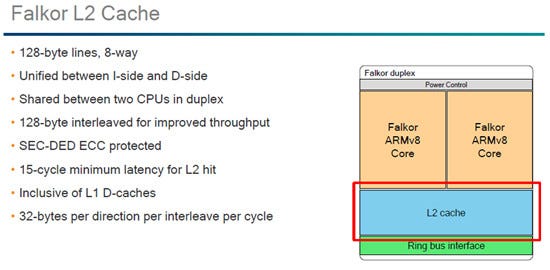

Falkor L2キャッシュは128バイトのキャッシュラインで、8way構成になっている。L2キャッシュは、I/D共通のキャッシュで、2つのFalkorコアからアクセスされる。L2キャッシュヒットの場合のアクセスレーテンシは最低で15サイクルである。

そしてL2キャッシュにはSEC-DED(1ビット誤り訂正、2ビット誤り検出)コードがつけられており、1ビットエラーは訂正、2ビットエラーは検出できるようになっている。

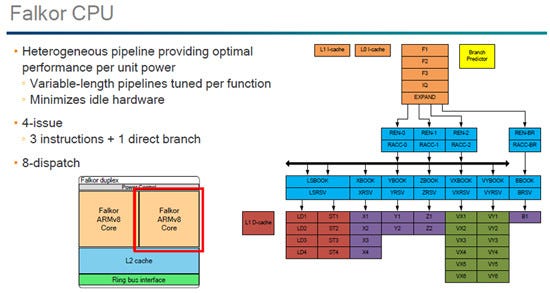

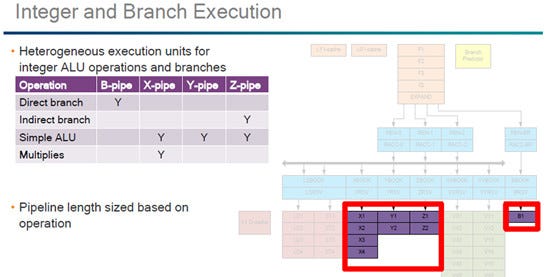

Falkor CPUは3つの演算やメモリアクセス命令と1つの直接分岐命令を発行できる4命令イシューのマイクロアーキテクチャとなっている。実行パイプラインはロード、ストア、整数演算などのX、Y、Zパイプと浮動小数点演算用のVXとVYパイプ、直接分岐用のBパイプラインの合計8本あり、最大8命令をディスパッチすることができる。

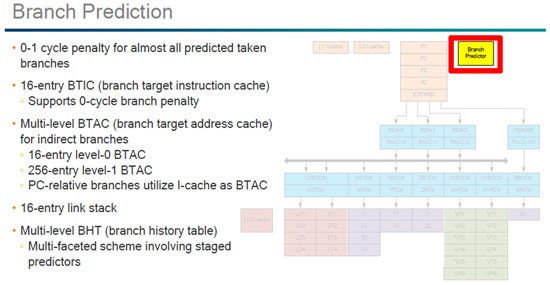

Falkorの分岐予測は、16エントリのBTICを持ち、ヒットした場合は分岐ペナルティはゼロである。そして、BTACは2階層になっており、レベル0は16エントリ、レベル1は256エントリとなっている。それに加えて、Call-Returnの処理用の16エントリのリンクスタックを持っている。結果として、殆どのTaken予測の分岐は0-1サイクルのペナルティーで処理できる。

また、BHTはマルチレベルになっている。

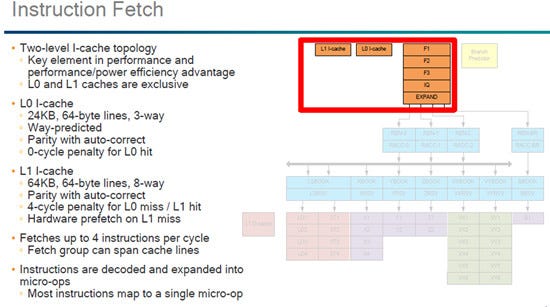

命令キャッシュは24KBのL0キャッシュと64KBのL1キャッシュがあり、L0命令キャッシュをヒットした場合は0サイクルペナルティで命令をフェッチできる。L0をミスし、L1命令キャッシュをヒットした場合は4サイクルのペナルティとなる。

命令キャッシュは読み出しオンリーであるので、パリティだけで、エラーが検出された場合はECCのついたL2キャッシュから読み直して訂正している。

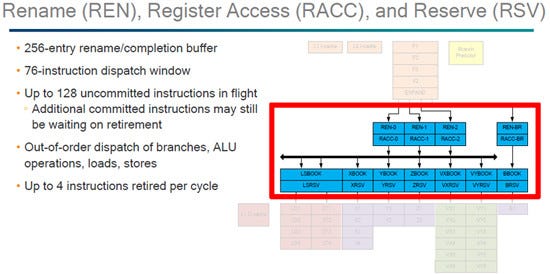

リネーム、レジスタアクセス系は、256エントリのリネーム/完了バッファを持ち、最大76命令をディスパッチできる。命令のディスパッチはOut-of-Orderで、インオーダ完了させることでIn Orderの実行と同じ結果を作り出す。この部分は普通の4命令完了のOut-of-Order実行エンジンという感じである。

整数演算命令と分岐命令はBパイプとX、Y、Zパイプで処理される。各命令タイプと実行されるパイプの対応を次の表に示す。

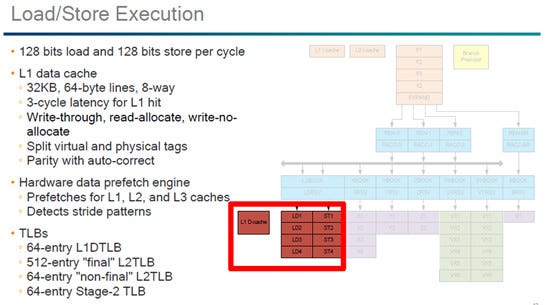

ロードとストアはそれぞれ1本のパイプがあり、毎サイクル128ビットのロードと128ビットのストアを実行することができる。L1Dキャッシュは32KBで8way、キャッシュラインサイズは64バイトである。L1Dキャッシュはライトスルーでライト時にはキャッシュラインをアロケートしない。ライトスルーであるので、パリティチェックでエラーを検出した場合はL2キャッシュから読み出してエラーを訂正する。

L1、L2、L3キャッシュはそれぞれのプリフェッチエンジンを持ち、プリフェッチエンジンはストライドの検出を行う。TLBは64エントリのL1DTLBと512エントリのL2TLBを持つ。

このFalkorコアの構造をみると、特別なことはほとんどなく、4命令実行の標準的なOut-of-Orderコアという感じである。