|

|

Hot Chips 29でFPGAベースのXPUを発表するBaiduのJian Ouyang氏 |

中国のWeb大手のBaiduは、Hot Chips 29において、FPGAベースのアクセラレータ「XPU」の発表を行った。Baiduは、2014年、2016年にもHot ChipsにおいてFPGAベースのSoftware Defined Accelerator(SDA)の発表を行っており、継続的な研究開発を行ってきている。

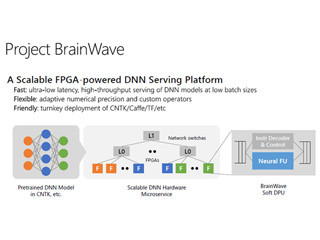

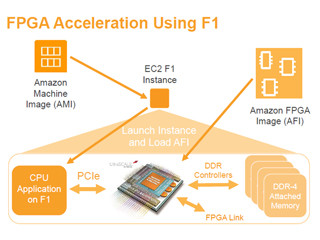

MicrosoftもProject CatapultでFPGAを使ったアクセラレータを開発し、データセンターへ展開して、Bingのサーチや翻訳の加速にすでに実用化している。また、AmazonはF1インスタンスというクラウド上でFPGAが使えるサービスを開始している。ということで、すでに、FPGAベースのアクセラレータは、大量のデータを処理するケースでは一定の地位を築いていると言える。

FPGAはAIのConvolutionや行列積の計算など、データ解析の分野では圧縮、伸長、フィルタなどの処理に向いている。また、MAC演算器を多数搭載しており、各種の計算に使用できる。さらに高速のメモリアクセスインタフェースを持ちバンド幅も大きい。ということで、FPGAはAIやビッグデータ処理にポテンシャルがあるという。

|

|

FPGAはAIやビッグデータ処理に必要とされる演算能力、高メモリバンド幅のインタフェースを持っており,これらの用途に向いている (このレポートのすべての図は、Hot Chips 29でのBaiduの発表資料のコピーである) |

これまでのFPGAアクセラレータは、特定のワークロード向けに作られており、効率は高いもののプログラムして広範な用途に使うことはできない。CPUは柔軟性は高いがAIやビッグデータの処理性能はあまり高くない。GPUは並列性の高い処理では高性能を発揮するが、処理によっては性能が出ない。

このため、大量の計算を行うワークロードとルールベースの処理の両方にまたがる広範なワークロードで、柔軟性があり、高い効率を発揮できるアクセラレータが欲しいということからXPUを考えたという。

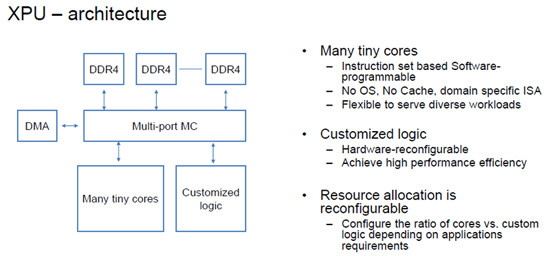

XPUは多数の小さなコアとカスタムロジックのブロックに、DDR4メモリをマルチポートのメモリコントローラで接続した構造になっている。そして、データの転送をおこなうためのDMAを持っている。

多数の小規模コアは、命令セットを持つプロセサで、プログラム可能で、広範なワークロードを処理する柔軟性を持っている。一方、カスタムロジックはハードウェア再構成で作る専用ロジックで高い性能と効率を実現する。

多数の小規模コアの部分は、次の図のようになっている。右側に描かれたコアクラスタは32個のコアとSFA(Special Function Accelerator)と32KBのシェアードメモリを持っている。そして、左側の図のように、FPGAの集積度に応じて、多数のコアクラスタが作られ、マルチポートのメモリコントローラに繋がれている。

小規模コアはMIPSに似た命令セットを持ち、4段のパイプラインで命令を実行する。条件分岐の処理を高速にするため、BHT(Branch History Table)を使って分岐予測を行っている。

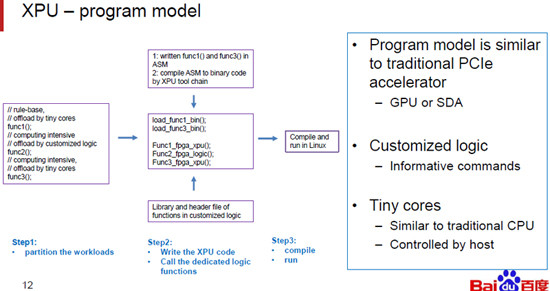

XPUをプログラムするには、まず、Step1でどの仕事をどこでやるのかというワークロードの分割を行う。そして、Step2では、小規模コアのクラスタで処理を行う部分のアセンブラプログラムを書き、専用のカスタムロジックで処理する部分の呼び出しを行う。最後のStep3では、コンパイルを行い実行する。

なお、この図には書かれていないが、Step2ではカスタムロジック部をFPGAで設計する必要があると考えられる。

XPUの実装であるが、XilinxのVertex Ultra+シリーズのVU9P FPGAを使用している。1つの小規模コアは、1252LUTと1230FF、4DSPと5BRAMで作られており、256コアを作るのに、VU9P FPGAのLUTの25%、DSPの15%を必要としている。

ディープラーニング用のカスタムロジックは5120 DSPを使い、600MHzクロックで16ビットの整数で計算を行っている。この部分は6.144Topsの性能を持っている。