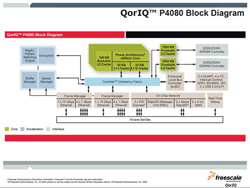

さて、そのQorIQ P4080の内部は? というとこんな形である。

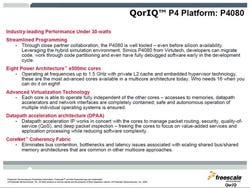

搭載されるコアはe500mcとなり、L2キャッシュはBackside側に移された。コア同士やL3キャッシュとの間は、新しいCoreNetというFabricで接続されるようになり、L3キャッシュは2MB搭載される。これに接続される周辺回路も凄まじく、PCIe×2、SerialRapid I/O×2、GbE×8、10GbE×2と、さらに様々なアクセラレータといったものになっている。主要な特長は以下のスライドの通りであるが、これが30W以下の消費電力、というあたりがこのプロセッサの特長を物語っていると考えてよいだろう。

|

|

e500mcの詳細とかVirtualization関連は後述。DPAAは、図の左にある4つのAccelerationを指す。こうしたものまで全部動かして、それで30W以下というのは、これはこれで驚異的な低消費電力であるとは思う |

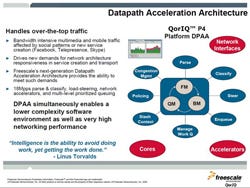

DPAAについては以下のスライドに概略があるが、L4以上のルーティングに必要とされるContents ProcessingやEncryptionをまとめたもので、「ソフトウェア構築の単純化に役立つ」としているあたりが、DPAAの目的を示していると考えて良いだろう。

|

|

パース性能が18Mpps(毎秒18万Parse)というあたりは、確かに壮絶な性能である。大雑把に平均20Bytes程度でMessageが構築されているとすれば、3.6Gbps程度の処理性能があることになる。もっとも10GbEを2本も持つP4080からすれば、これでもまだフルのWire Speedには至らないのかもしれないが |

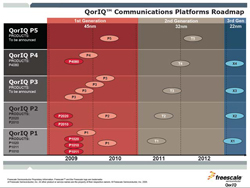

最後に今後のロードマップであるが、2009年中にまずP2、ついでP1とP4が投入される。そのP1/P4と同時期にP3がアナウンスされ、またP1/P4の後継製品がさらに登場するようだ。P5は2010年からの投入となるようだ。また2nd Genで32nm SOIではT1~T5と製品グループ名を変えて投入、その後は22nm SOIも視野には入れているようだが、この辺りになると先になりすぎるので今後随時計画は変更されてゆくと思われる。