Power.org Update

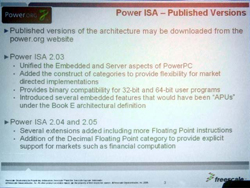

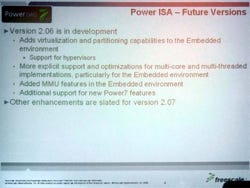

次にこれに関連して、Power.orgの動向をちょっとまとめておきたい。以前のレポートでもまとめた通り、2006年にはPowerISA 2.03が発表されたが、これに続いてPowerISA 2.04/2.05と開発が進み、今年第4四半期にはPowerISA 2.06が発表される予定だ。

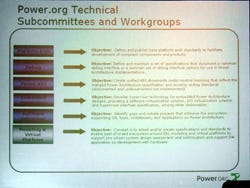

さてそのPower.orgの活動だが、基本的には以前とは大きくは変わらない。下のスライドは、一番下がH/W、一番上がApplicationとなるおなじみの階層構造で、ここに対してPower.orgがどんなSpecを提供しているのかをまとめたものである。

具体的に現在Power.orgでは以下の6つのTechnical Subcommittees/Workgroupが活動しており、セッションではこの各項目について簡単に説明が行われた。

|

|

上から順に"Platform Arch."、"Debug"、"Power ABI"、"Embedded Hypervisor"、"Software Initiatives"、"Modeling & Virtrual Platform"となる |

まずPlatform Architectureについてであるが、2.03→2.06への変更点がまとめられている。2.07は来年以降ということで、まずはこの2.06が1つのスタンダードとなるようだ。

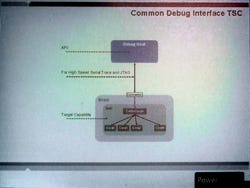

次のDebug、基本的にはDebug用高速I/Fを新規に追加することで、特にマルチコア環境におけるDebugの自由度を高めようという話だ。

例えばP4080の場合、各コア(と、下手をするとAccelerator)に個別にJTAG/Trace Lineを繋いでいたらきりが無い。そこで、複数のコアのJTAG/Traceをまとめて接続できる高速Debug I/Fを追加するというものだ。

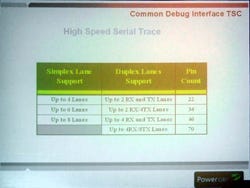

Power.orgではこれをCDI(Common Debug Interface)と呼んでいるが、問題はこのリンク、転送速度は何と6Gbpsで、最大12Lane(4RX/8TX)にもなることだ。ここにJTAGとTraceを通す事から、データを扱いやすくするためにDebugging APIをFrameworkの形で提供するとの話であった。