e500mc

さてそのe500mcはどうe500コアから変化したか、というあたりをもう少し説明したい。基本的に言えば、e500mcコアはe500コアをベースに、マルチコアの対応を施したものという事になる。ただe500そのものもDual Coreには対応しているわけで、「では何が拡張されているのか?」という話になる。見た目にはInterconnectとのI/F、それとL2キャッシュの持ち方が変わった(というか、L2キャッシュをオンコアで搭載した)事が大きな違いだが、細かく見るともう少し異なった話となる。

ベースとなったのは、e500v2ということらしい。e500v2は昨年のレポートでも触れたが、基本的にはe500のマイナーアップデートといったところである。

基本的にはPowerISA 2.0準拠を目指したもので、User ApplicationはPowerPC Classicと互換性があるが、OSなどのSystem Programについては、MMUの構造を始めとして随所に変更点があるので、かなりの変更が必要となっている。これをベースに、PowerISA 2.06 Embedded準拠とし、CoreNet Fabricをサポートしたのがe500mcということになる。

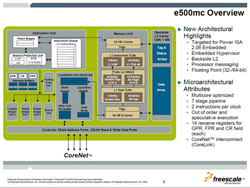

内部構造は以下のような形で、従来のe500コアとの違いはL2キャッシュとInterconnectということになる。

|

|

L2は最大1MBまでと書いてあるが、技術的には4MBまで可能だそうだ。それだけのTag/Status Arrayを拡張できる余地が残してあるということだろう。InterconnectはCoreNetに繋がるCoreLinkと呼ばれるI/Fに取って代わられた。データ幅は128bitと従来から倍増している |

もう少し細かな違いはというと、こちらだ。

汎用レジスタは32bitのみとなり、またFloating Pointは全てFPUで扱うことになり、Embedded Floating Point関係が削除されたほか、System Registerの一部が省略されている。変更点は、L2のサイズやInterconnectに関連する部分が主である。