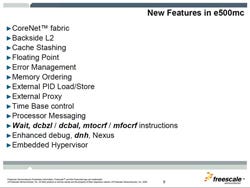

では追加は? というと、これが意外に盛りだくさんである。

|

|

最初の2つはすでに述べた話。L2の持ち方が変わるのに伴い、Stashingの機能が追加されたり、Embedded FPUではなくFPUが追加されたり、その他も色々ある。ただ個人的には、一番大きな影響があるのは最後のEmbedded Hypervisorではないかと思う |

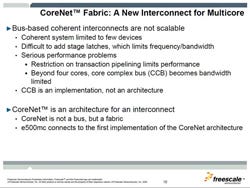

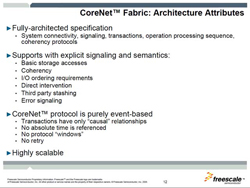

まずCoreNet fablicの説明はこちらである。

これは今回新規に開発したそうで、説明では"BusではなくFabricである"ことを強調していた。もっとも、それでは具体的にどんなインプリメントなのか? という話は今回はまだ未公表であった。

とはいえ、トランザクションの管理は比較的ルーズのようだし、いわゆる"Window"もなければリトライもなく、Error Signalingだけがあるという事は、つまり通信エラーのハンドリングは上位層任せという事になる。ここから考えると、CoreNetは丁度OCPの様に、SoC内部のInterconnectだけを考えており、MCMなどのSIPパッケージまで展開するつもりは現状無さそうである。

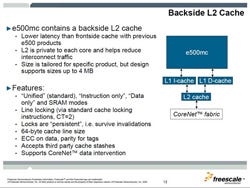

次にL2キャッシュ関連だが、これはコンサバティブな構成である。

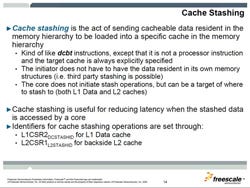

ただ、Unified/I-Only/D-Onlyを外部から指定できるのは面白いし、Cache stashingをサポートしているのはいかにも通信用プロセッサという気がする。Cache stashingとは、Cache Missを防ぐ技法の1つ。例えばGbE MACからパケットがCPUに送られた場合、それをメモリに格納するのではなく、直接キャッシュに送り込んでしまう。MACからパケットが送られる場合、当然割り込みがMACからCPUに送られる。これを受けてCPUの割り込みルーチンがパケットをチェックしようとしても、パケットがメモリに格納されているとCache Missが発生し、結果として割り込み処理が遅くなる。Cache stashingを使うとこのCache Missを防げるという仕組みだ。e500mcでは、このStashingをサポートするための専用レジスタが設けられ、これで管理を行うことになっている。

|

|

本来L1とかL2はCPU Coreが直接管理するもので、外部から(まるでDMAの様に)データを転送される事はあまり考えていないが、用途によってはこうした技法が非常に効果的である。ちなみにプレゼンテーションで3rd partyと書いているのは、この場合で言えばCoreNet経由で繋がったFrame ManagerとかOn-Chip Networkを指す |

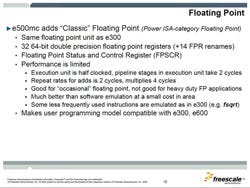

FPUは逆に、ちょっと先祖帰りしている。敢えてe300/e600というClassic PowerPCと同じFPUを搭載し、e500v2で搭載したEmbedded FPUを削除した、というあたりは、e500mcの、というよりはQorIQの使われ方を示しているように思える。

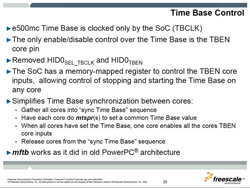

Time Base Controlもちょっと面白い。

|

|

TBENの設定で、任意のコアをTime Baseで動作させられる、というあたりがまた独特である。8コアのうち2コアは独立に処理をさせ、残り6コアがTime Baseで動作するなんて事が、これで簡単に実現できる |

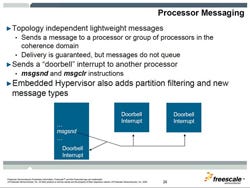

あくまでもSoCを前提にしての機能、というのはSiPなどでは遅延が大きすぎて同期が取れないという事なのだろうが、複数個のコアを同期させるというニーズが必要ば場合に役立つと思われる。またプロセッサ間の同期のために、"Doorbell Interrupt"が新たに追加されている。