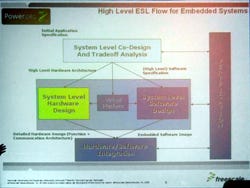

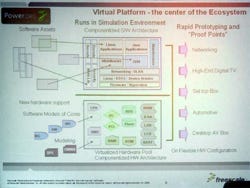

次はちょっと順序が変わってVirtual Platformである。要するに実際にSoCを作ってからソフトウェアの開発をするのでなく、仮想化環境の上でCPUコアと周辺回路を組み合わせた「仮想SoC」を作ってその上で開発を行うことで、開発期間の削減やSoCデザインの設計/チューニングに役立てよう、というものだ。

|

|

この部分の説明はVirtutechが行った。同社はPowerPC向けのSolutionを用意しており、すでにP4080に対応したVirtual Platformもアナウンスしている。そんな事もあってか、半分位は同社の商品説明になっていた気も |

このVirtual PlatformはVirtutechのSimicsと呼ばれるシミュレーション環境上で動くもので、この上でハードウェアの構成レベルから変えながらソフトウェアをインプリメントしてゆくことで、例えば必要とされるパフォーマンスを検討したり、Acceleratorを入れるか否かを判断したり、なんてことも可能だし、SoCの構成が決まった後は実際にシリコンが出てくる前にSoftwareの動作テストをSimics上で行うことで開発期間の短縮に繋がる。またデバッグもSimics上で併用することで、細かく動作検証をしやすいといったメリットが語られた。

|

|

まぁそれは分からなくもないのだが、問題はSimicsそのものの値段如何といったあたりだろう。この手のSimulationは当然猛烈に遅いわけで、Virtutechもこれを高速化するSimics Acceleratorをリリースするが、「8コアのホストを64個繋いだシステムを使うと、10倍高速化できる」というあたり、初期投資がどの位必要かを考えると、本当にこれが賢明なアイディアなのか、にわかに判断できない |

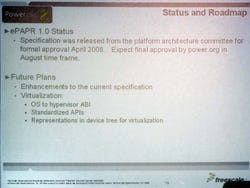

次がePAPRである。ePAPRとは要するにPowerPCのブートプログラムに関するStandardと考えれば良い。

位置づけとしては、x86のいわゆるBIOS(Legacy BIOS)やEFI、SPARC系とかMacのOpen Boot PROMなどと同じものと考えれば良いだろう。これらのものと比較して異なる点は、当初からMulti-CPUやHypervisorを考慮している点だ。

|

|

とはいえ、ePAPRそのものがHypervisorとなったりはしない。あくまでもePAPRはSingle CPUで動作し(これをboot CPUと呼ぶが、これがどう決まるのかは不明)、残りのCPUはsecondary CPUという扱いになる。secondary CPUはboot CPUから(Boot loaderやそれに続き起動されるHypervisorなどで)起動される形だ |

この目的で、システム内部のコンポーネントを一覧で取得できるDevice Treeをサポートしている。今後は、さらにHypervisor周りを拡張したりする予定があるようだが、当面はこのePAPR 1.0で利用されることになるだろう。

|

|

OS to hypervisor ABIなんて項目がある辺りは、今後はePARAはブート時のみならずHypervisorやGuest OSをロードして実行が開始された後も介在することを意図しているようにも読める |

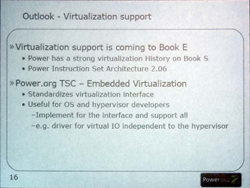

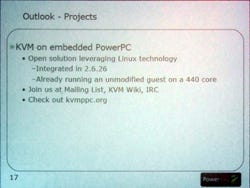

最後にVirtualization関係である。基本的な構造は先ほどe500mcのところで説明したとおり、Partitioningと併用する形でのVirtualizationがPower ISA 2.06で盛り込まれており、これは最終的にBook Eに盛り込まれる形になる。面白いのはこれとは別にHypervisorを使うKVM(Kilo Virtual Machine)がすでに動作していることで、今後はBook E 2.06へのインプリメントを進めると表明していることだろう。

|

|

|

Book SはIBMのサーバ向けのSpecificationで、当然こちらでは長くVirtualizationがサポートされてきた。こちらはEnterprise向けとあって、非常に強力ではあるが、実装も非常に重厚で、Embedded向けには適さない。これについてはwikiを見ていただいた方が早いかもしれない。KVMは機能的にはそれほど多くないが、それでもEmbedded向けには十分な能力を持っている |

|