韓Samsung Electronicsは8月13日、同社の製造受託部門であるSamsung FoundryのEUVリソグラフィを使用する7nmおよび5nm ロジックデバイス向けに独自の3D ICパッケージング技術「eXtended-Cube(X-Cube)」の提供を開始したと発表した。

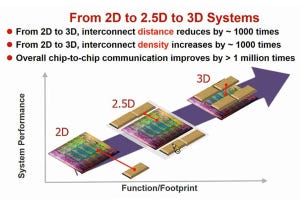

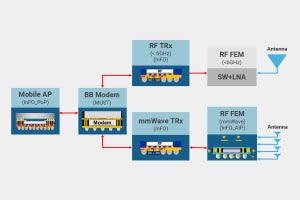

X-Cubeは、同社のシリコン貫通ビア(TSV)テクノロジーを活用して複数のチップを垂直に集積し結線することにより、速度と電力効率を向上させ、5G、人工知能、HPC、モバイルおよウェアラブルなどの次世代アプリケーションの厳しいパフォーマンス要求への対応を支援するという。

X-Cubeを使用すると、チップ設計者は独自の要件に最適なカスタムソリューションを構築するための優れた柔軟性を享受できるという。7nmプロセスを用いて製作されたX-Cubeテストチップは、TSVテクノロジーを使用してロジックダイの上にキャッシュメモリの役割のSRAMをスタックし、スペースを解放してより多くのメモリを小さなフットプリントに詰め込むことができたという。3D集積により実現された超薄型パッケージ設計は、ダイ間の信号経路を短縮し、データ転送速度とエネルギー効率を最大化するため、顧客は、メモリの帯域幅と密度を希望の仕様に合わせて調整することもできるという。

Samsungのファウンドリマーケット戦略担当VPのMoonsoo Kang氏は「Samsungの新たな3D集積技術は、最先端のEUVプロセスノードでも信頼性の高いTSV相互接続を保証している。私たちは、半導体の境界を押し広げる可能性のある3D ICイノベーションをさらに提供することに取り組んでいく」と述べている。

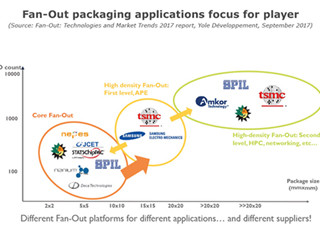

Samsung Foundryは、世界中のファブレス顧客と協力し、次世代の高性能アプリケーションでの3D ICソリューションの導入を促進することにしているという。EUVリソグラフィ採用の超微細化プロセスによるロジック量産では歩留まりが低迷し、TSMCに顧客を奪われかねないSamsungは、3Dパッケージングの付加価値で顧客をつなぎ留めたいようである。

なお、Samsung X-Cubeの技術の詳細は、8月16〜18日にオンライン開催されるハイパフォーマンスコンピューティングに関する年次国国際会議「Hot Chips」にて発表される予定となっている。