米Intelは米太平洋時間の4月2日午前9時30分より、「DATA-CENTRIC INNOVATION DAY」と呼ばれるイベントをサンフランシスコで開催する。恐らくはこのイベントの中で発表されると思われる10nmプロセスを利用したFPGAに関して、事前説明会の形で紹介が行われたので、この内容をお届けしたい(Photo01)。

Intel 10nmプロセス採用のFPGAが遂に登場

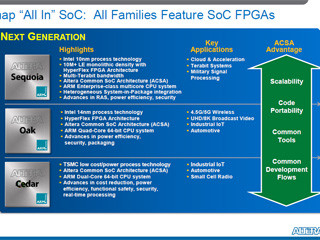

さて、元々Intelに買収される以前の2015年におけるAlteraのロードマップでは、Stratix 10の後継となるハイエンドにIntelの10nmプロセスを利用した「Altera Sequoia」、Arria 10の後継となるミドルレンジにIntelの14nmプロセスを利用した「Altera Oak」を、Cyclone V(まだこの当時はCyclone 10の話は無かった)の後継となるローエンドにはTSMCのプロセス(具体的には未公表)を利用した「Altera Cedar」がそれぞれ予定されていた。ところが2015年末にAlteraがIntelに買収されたことで、このあたりのロードマップが刷新。2016年におけるロードマップでは、ハイエンドが10nmを利用するFalcon Mesa HE(High End)、ミドルレンジが同じく10nmを利用するFalcon Mesa(MR)、ローエンドがIntelの22nmを利用したHarrisvilleになる、という具合に変更になった。

問題はこの10nmプロセスの立ち上げにIntel自身が失敗したことで、当初予定から3年遅れで今年やっとなんとか量産が立ち上がろうとしている(*1)状況である。その間に競合であるXilinxはTSMCの7nmプロセスを利用したVersalシリーズを発表しており、Intelとしてもこの分野へのテコ入れを急ぐ必要があった。

筆者注:(*1) 一応2018年にはCannon LakeベースのCore i3を出荷しているので、建前上は2018年に10nmが立ち上がったことになっているが、これはアリバイ工作的なもので、現実問題としては10nmが立ち上がったうちに入っていない。

そうした事もあって、Intelは2018年12月にサンタクララで開催されたIntel Architecture Day 2018で、そのFalcon Mesaの試作品を利用した112G PAM4 PHYの動作デモを行っている。そんなわけで、あとは10nmプロセスがいつ利用可能になり、いつ出荷開始されるかが最大の焦点になっていた訳だ。

今後のIntel FPGAのブランド名となる「Agilex」

これまでの背景を踏まえた発表内容であるが、そのFalcon Mesaがこの度改めて、「Agilex(アジレックス)」というブランド名で提供されることが明らかにされた(Photo02)。

-

Photo02:AgilexはFalcom Mesaのブランド名ではなく、要するに現在のStratix/Arria/Cycloneの次の世代の製品全体の総称ということになる。このあたりはIntelのNaming Ruleにあわせた形か

そのAgilex FPGA、その最初の製品であるFalcon Mesaの特徴がこちら(Photo03)。

単に10nmプロセスで実装した以外に、色々な特徴が追加されている事が明らかにされている。これをスライドの順に説明していきたい。

Photo04がそのFalcon MesaベースのAgilex FPGAの特徴である。

まずFabricそのものであるが、第2世代のHyperFlex Architectureという表記から判るように、基本的なFPGAの構成は、既存のStrarix 10に搭載されている様にALM(Adaptive Logic Module)をベースにしたLAB(Logic Array Block)とMLAB(Memory LAB)をベースにし、さらにHyper-Registerを利用した配線制御を可能にするといった形になっており、これに関しては特に変更が無いという話であった。

ちなみにDSP性能が最大40TFlopsとされるが、Agilex FPGAのDSPブロックは1cycleあたりFP16の演算を2つ可能とされており、DSPブロックの数×動作周波数×2=40Tになる、という計算だそうだ。Strarix 10の世代ではFP32で最大10TFlopsとされており、ラフにいって倍の処理性能になった事になる。ちなみに第2世代になってHyperFlex Architectureがどう変わったのか、は現時点では未公開である。

外部のメモリとしてはHBMおよびDDR5のサポートが掲げられているが、HBM2はまだしもDDR5については普及が事実上2021年あたりになりそうで、それもあって最初の製品はDDR4のサポートになる(両対応、という事の模様)。このDDR4/HBM2のI/FはFPGA Fabricと同じダイに内蔵される。Optane DCについては、I/FはおそらくDDR4を流用し、単にそのサポートが追加されているという話と思われる。

さて外部のI/Fであるが、先に紹介した112G PAM4 PHYに加えてPCIe Gen5とこれを利用したCXLまで搭載されることが発表された。ただこれらのPHY(や恐らく通常のGPIOなど)は、いずれもEMIBを利用してFPGA Fabricとは別のダイの形で実装されることになる。図で言うところの"Other Chiplet"に関してはおそらく作りやすいプロセス(14nmないし22nm)だが、112G PHYやPCIe/CXLについては10nmプロセス(ただしFPGA Fabricとは構成が異なるもの)で製造されるとの事だった。

またパッケージング(Photo05)であるが、当初はEMIBを利用した2.5D Packageの形になるが、将来的にはFoverosについても「可能性は否定しない」との事だった。ここにeASICでのDevice Tileが載っているのは、将来のAgilex FPGAの中には、eASICのダイを最初から実装可能なパッケージが用意されており、ここにカスタマイズしたeASICのダイを搭載する、セミカスタムFPGAとでも呼ぶべき製品が考慮されているのかもしれない。

-

Photo05:eASICの話は後述。ちなみに112G PAM4 PHY以外に58G PAM4のPHYも当然ラインアップされるが、こちらは10nmではなく14nm辺りでの製造になるのかもしれない。ちなみにIntel自身はEMIBを3D Packageと分類している

そのeASICとのかかわりがこちら(Photo06)。理屈で言えばeASICのソリューションはXilinxおよび旧AlteraのFPGAで動いていたものをそのまま移植して稼働させることが可能だったので、プロトタイプをAgilexで作り、量産をeASICで、というシナリオは無い訳ではないが、Stratix 10もそうだがAgilexなどではFPGA Fabricはともかく周辺回路が全然違うため、現実問題としてそのまま移植するのは難しい。このあたりについては「確かに現行のeASICはTSMCで製造しており、Agilexとの互換性は無い。ただ次世代のeASICには期待してほしい」という回答であった。

次がI/Oについて(Photo07)。Intelは今年3月11日に、突如としてCXLというCache Coherency Interconnectを発表した。これの普及のためにCXL Consortiumも同日設立している。

このCXLはPCIe Gen5の上にCahce Coherency Protocolを実装するという仕組みになっており、色々と疑問は多い(この辺の技術については、近いうちに別の記事としてまとめてお届けしたいと思っている)のだが、それはともかくとしてIntelとしては将来のCPU/FPGAのInterconnectをこのCXLに一本化するつもりの様だ。

ただそのためにはFPGAだけでなくCPU側もPCIe Gen5に対応する必要がある訳で、実際にCXLが利用できるようになるには最短でも1年以上、現実問題としては2年以上先になると思われる。それまでの間はPCIe Gen4での接続になるだろう。

さてFPGA Fabricに関しては詳細は語られていないが、DSPについては若干の補足があった(Photo08)。

新しくFP16に加えてBFLOAT16をサポートするほか、INT2のサポートも追加されている。またこれに向けてOpenVINO Toolkitが用意されることになる。

開発環境(Photo09)としてはQuartus PRIMEの他、One APIでのサポートがあるとされるが、このOne APIとはやはり昨年12月のIntel Architecture Day 2018で登場した「CPU/GPU/FPGA/Acceleratorなどを1つのAPIでまとめて扱えるようにする仕組み」である。こちらはまだ具体的な話が無いので何とも言えないのだが、一応2019年中には一般公開される予定となっており、Verilogで直接記述したければQuartus PRIMEを、高級言語で記述したければOne APIを、という形で考えているものと思われる。

さてそのAgilexであるが、最初に説明した様にこの名称はブランドであって、複数のグレードを内包する予定だが、当初出てくるものはStratix 10の後継という位置付けになる。その最初のAgilexだが、F/I/Mという3種類のシリーズが予定されている(Photo10)。

ここにもあるように、最初のデバイス提供(これは要するにリードカスタマへのアルファサンプリングの意味)が今年第3四半期であり、恐らくはFシリーズと思われる。この世代ではPCIe Gen4とDDR4で、これはIce LakeベースのPlatformで利用することを念頭に置いていると思われる。

ちなみに今回の発表では、量産出荷(General Available)の時期は明確にされなかったが、「一般的に言えばリードカスタマへのアルファサンプリングから1年後だろう」と説明された。デスクトップ向けのCoreシリーズはともかくとしてXeonに関して言えば、Ice Lake世代の製品提供は2020年が予定されており、これと丁度歩調も合うところだ。これに続いてIシリーズとMシリーズが順次(おそらく2021年~2022年に)提供されていくという感じになるだろう。というのは、I/MシリーズではPCIe Gen5とCXLがサポートされるが、これに対応できるコアは2020年のWillow Cove(Tiger Cove)か、下手をすると2021年のGolden Cove(Alder Lake)まで待つ必要があると思われるためだ。

説明会ではこのAgilexを利用したアプリケーション例もいくつか説明された。Photo11はNFVなどを前提にした構成で、Xeon単体では実現できない高い処理性能をAgilexとの組み合わせで実現できるとする。

Photo12はデータセンター向けソリューションで、様々なアプリケーションがより効率よく処理できる(その最大の理由はFPGAとCPUが共通のメモリをCache Coherencyを保ってアクセスできることになる)とする。

5Gに関してはPACですでに対応を表明している訳だが、これをさらに高性能化できる、としている(Photo13)。

-

Photo13:理屈ではeASICを使って消費電力とコストの最適化が可能なのは事実だが、昨今の動向を見ているとFPGAのままにして柔軟性を保持する方向にトレンドが進んでおり、果たしてこのニーズがどこまであるのか正直良く分からない

またサーバのアクセラレータとしての利用(Photo14)も主要な用途として挙げられている。ただこうしたアクセラレータとしての利用を考えるとPACカードでの提供が考えられる訳だが、現時点でAgilexを搭載するPACに関してはノーコメントであった。量産開始が1年以上先の話であることから、現時点でPACの議論は時期尚早ということだろう。

ところで冒頭に述べたようにAgilexはStratixだけでなく、将来はArriaあるいはCycloneのグレードの後継製品も包括するという話であったが、これらについても10nmでの提供になるのか、あるいは既存の14nmのままAgilexを名乗るようになるのかは今のところはっきりしない。

さらに言えば「CPLD(HardCopy II)は対応外だが、FPGAはすべてAgilexに包括される。MAXシリーズはFPGAだ」という話で、ここにはMax 10の後継製品も含まれる(!)という話である。

ただ既存のSRAMベースのArria/CycloneはともかくFlashベースのMAXをどうするつもりなのかは現時点では不明である。可能性としては22nm+MRAMプロセス、という案も無くはないのかもしれないし、MAXもSRAMベースに代わるのかもしれないが、このあたりもまだ不明なままだ。恐らく今年後半に入ると、もう少し詳細な情報が出てくるのではないかと思われる。