NTTは4月23日、室温で動作するDRAMセルにおいて、熱とエントロピーを電子1個単位で同時に測定することに成功したと発表した。電子数の変化を単電子スケールで検出可能なNTT独自のナノメートルスケール電子デバイスを用いることで、これまで評価が困難だった実用メモリ素子における情報処理の熱力学的特性を直接測定することを可能にした。

同成果はNTT物性科学基礎研究所の清水貴勢氏、知田健作氏、山端元音氏、西口克彦氏らによるもの。詳細は2026年3月20日に、米国学術誌「Physical Review Letters」に掲載された。

情報処理と熱力学の原理的限界を探る

生成AIの普及に伴い、情報処理に必要な電力消費の増大が深刻な課題となる中、近年、情報と熱力学の関係が注目されるようになっている。

例えば、データの保持役であるDRAMにおいては、0と1でデータが示されるが、そうしたばらついた情報を一定の状態(すべてを1もしくは0にする)にそろえる初期化操作が行われることとなる。その際、情報のばらつきを表すエントロピー(情報エントロピー=シャノンエントロピー)が減少する一方、その代償でエネルギーの消費が発生し、それが熱として放出される。この情報処理におけるエネルギー消費の理論的最小値は、熱力学第二法則に基づく「ランダウア限界」に由来すると考えられている。

ランダウア限界は、1ビットの情報を削除する際に、必ず最低限の熱エネルギーが生じるという法則であり、理論上は絶対零度に近い極低温環境下で、非常にゆっくりと時間をかけて作業をすると、限りなくゼロに近づけられているといわれているが、実際の電子デバイスのエネルギー消費においては、この限界と大きく乖離してしまった状態であり、その差がどこに起因するのかはよく分かっていなった。

仮説レベルとしては、高速な処理や周辺回路の影響などが考えられてきたほか、実際に実験的な検証は行われてこなかったという。

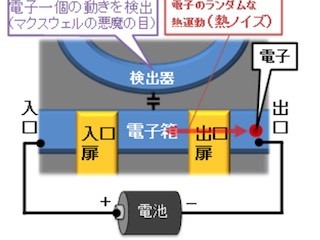

NTTでは、2017年にはマクスウェルの悪魔を用いた発電の実証を報告していたほか、研究チームは2024年に、DRAM等価回路を持つシリコンメモリの情報消去時の発熱を測定し、ランダウア限界に達しないことを発見したことを報告するなど、謎を解き明かすべく、さまざまな研究を行ってきた。今回の研究では、そうした取り組みの一環として、高速処理や周辺回路の影響を排除することを目的に、1T1C(1Transistor+1Capacitor)構造のDRAMセルを用いて、低速で初期化操作を行った際にランダウア限界に到達できるのかの検証に挑んだという。

この目的の達成のためには、DRAMセルで生じる発熱量や情報の初期化の際のエントロピー変化を測定する必要があるが、ランダウア限界に近い極限条件においては、生じる発熱やエントロピーの変化を示す信号は雑音に埋もれてしまうほど小さいため、従来の手法では、特に室温環境下においては測定する方法がないことが課題であった。

キャパシタの電荷量を単電子単位の分解能で測定

そこで今回の研究では、この課題解決を図るべく、独自のシリコンナノデバイスを活用した単電子検出技術を応用する工夫を実施。具体的には、リード(ビット線)からトランジスタを経由してキャパシタに電子が到達する際のリードとキャパシタの間の電位差が発熱や吸熱を生み出すことから、この電位差を計算することができる高精度な検出器を組み込むことで、微小な信号の増幅を実現。キャパシタの電位を電荷量を算出することと、外部の印可電圧であるリード部の既知の電圧を組み合わせることで熱の算出を実現したという。

-

今回の研究の全体像。DRAMセルのキャパシタ部に併設する形でオンチップで検出器を作成。キャパシタの電荷量が変位した際に、検出器を流れる電流値の変化を読み取ることで、電子数の変化を読み取る仕組みを活用して、熱量とエントロピーを算出できるようにしたとする (出所:NTT)

キャパシタの電荷量は単電子単位の分解能で測定できているため、その電子数の確率分布からエントロピーの算出ができるようになり、これらを組み合わせることで熱とエントロピーを単電子単位で測定することが可能になったとする。

-

1T1CのDRAMセル構造のイメージ。一般的にはトランジスタの左側(ソース)がビット線、トランジスタ上部(ゲート)がワード線につながっており、ワード線でトランジスタの制御で、キャパシタの充放電を制御する。ワード線がオンの時かつビット線もオンの時、トランジスタがオンとなり、キャパシタに電荷が蓄えられる。逆にワード線をオンとして、ビット線をオフ(0V)とすると、キャパシタから電荷が放出される。情報の初期化は、いわゆるこのキャパシタの電荷の状態をすべて同じにする作業となる (出所:NTT)

実際の実験では、情報の初期化に伴うエントロピーと熱の測定を実施。具体的には、DRAMセルにおいてはキャパシタに蓄えられた電荷量に応じて情報が蓄えられることとなるが、初期化(この場合は、すべてを「1」にする)前は電荷がばらついた状態であり、その状態から初期化を図ると、注入する電荷量が少ないと熱揺らぎによって「0」が生じたままのエラーがばらつきとなる。この場合、エントロピーは小さくなるわけだが、注入される電荷量を変化させた際の初期化におけるばらつきの変化から、エントロピーの減少量を算出したところ、エントロピーが減少するほど発生する熱量が増えていくことが判明。つまり、初期化によるエラー率が減少していくほど、熱量がランダウア限界より離れていく性質があることがDRAMセルにはあることが示され、高速処理や周辺回路の影響だけで、こうした乖離の原因を説明できないことが示唆されたとする。

-

DRAMセルの構造と測定手法のイメージ。(a)はDRAMセルの等価回路、(b)は実際のDRAMセルの電子顕微鏡写真、(c)は検出器電流の測定例。キャパシタの電子の数の変化が、検出器電流の離散的な変化として現れる、(d)は電子の移動ごとに生じる熱量のグラフ。縦軸の単位は27℃における熱エネルギーkBT=25.9mV、(e)は熱量の算出方法を示した模式図 (出所:NTT)

これを熱力学的に考察すると、DRAMセルは熱的に不安定な状態に情報が保持されていて、初期化の過程で安定状態に移行する際に余分な発熱が生じてしまいランダウア限界に到達できないという結論に至ったとする。この結論を踏まえ、研究チームではランダウア限界に迫るようなデバイスを作るには、熱的に安定した状態に情報を保持できるような仕組みにする必要があることが示されたとする。

-

エントロピーの減少量と平均累計発熱量の測定結果の関係性。縦軸の単位は32℃における熱エネルギーkBT=26.3meVで、ΔSはエントロピー減少量。この図は、エントロピーの減少量が増加=初期化がうまく行けば行くほど、ランダウア限界から乖離していく性質がDRAMセルにあることを示す結果を現すものとなっている (出所:NTT)

メモリの省エネルギー化の実現に期待

研究チームでは、今回の研究で開発された技術は1T1CのDRAMセル以外の回路構造にも応用可能であるとしており、DRAMセル以外の情報処理回路に応用することで、省エネルギー性に優れた回路の開発につながることが期待されるとしており、研究チームとしてもDRAMセルを省エネルギーで駆動できる方法として、キャパシタ構造の最適化やプロセス線幅の最適化、印可電圧の高精度制御などといった次世代回路アーキテクチャの探索などを行っていきたいとしているほか、熱揺らぎを計算資源として活用する新たなコンピューティング技術の実現などを目指すとしている。