半導体研究機関であるベルギーimecは、米サンフランシスコで開催された半導体デバイスの国際会議「IEDM 2018」にて、FinFET構造の延命に向け、FinFETの積層構造技術に関する研究結果を発表した。

この積層技術は「Sequential-3D integration(S3D)」と呼ばれるもので、デバイスを形成した単結晶シリコン基板上にデバイス形成のための単結晶シリコン層を逐次積層していくという技術。SOIメーカーのSoitecが有する「Smart Cut技術」を応用することで実現する。

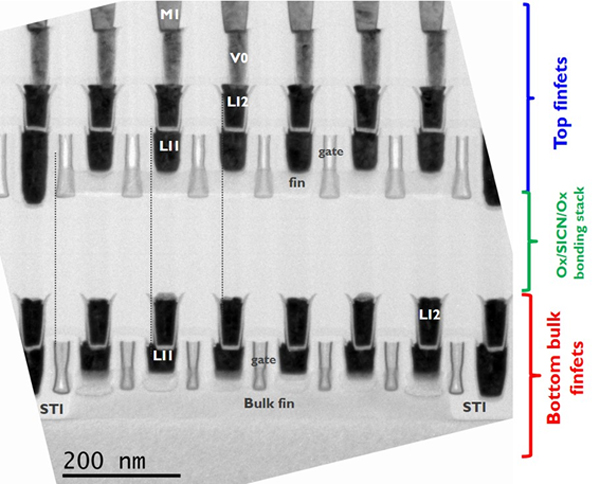

今回の研究では、同手法を用いて、45nmのフィンピッチと110nmのポリピッチ技術による300mmウェハ上での3次元積層FinFETの作製に成功したという。

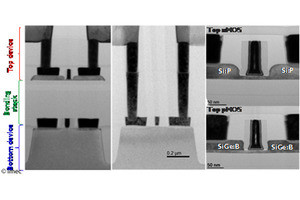

具体的には、まず、シリコン単結晶ウェハ上にボトム層(下層)にFinFETを形成。その後にS3Dを用いてトップ層となる単結晶シリコンを形成。それをウェハ間ボンディング技術でボトムデバイスの上に525℃未満の低温にて積層することに成功したという。

S3Dは、デバイス層を順次形成し、それを積み上げていくことで、チップ面積当たりのデバイス密度を高め、かつ異なるプロセスでのデバイスの集積を可能にするものだが、これまではトップ層にデバイスを形成するための処理温度が高すぎると、ボトム層のデバイスや相互接続層、ウェハボンディング用の絶縁層などの性能に悪影響を与える可能性が指摘されていたほか、低すぎればトップ層のデバイスの性能が低下する可能性が指摘されていた。

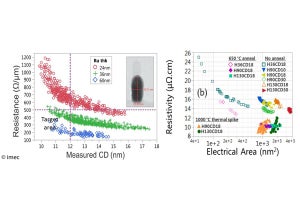

実際の性能としては、トップ層のデバイスは、高温処理で製造された低スタンバイ電力(LSTP)向けFinFETと同等の性能を示したとのことで、これにより高性能向けのボトム層のデバイスと、低消費電力やアナログに向けたトップ層のデバイスを組み合わせることができるようになるとimecでは説明しており、超微細なプロセスを活用しつつ、従来以上にデバイスの密度を上げるためにS3Dが有効なアプローチであることが確認されたとしている。