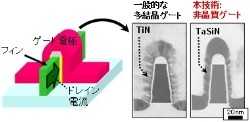

産業技術総合研究所(産総研)は12月15日、立体型トランジスタ(フィンFET)の低周波ノイズをこれまでの最小レベルに低減する技術を開発したと発表した。

同成果は、同所 ナノエレクトロニクス研究部門 シリコンナノデバイスグループの松川貴上級主任研究員、昌原明植研究グループ長らによるもの。詳細は、12月15~17日に米国サンフランシスコで開催される国際会議「2014 International Electron Devices Meeting(IEDM 2014)」にて発表される。

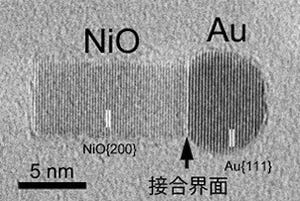

トランジスタの低周波ノイズはフリッカノイズとしても知られ、トランジスタの面積に反比例して増加するため、アナログ集積回路の縮小の妨げになっていた。また、寸法を小さくすることにより性能が向上したトランジスタをアナログ集積回路で活用する際の障害になっていた。今回、均質な状態が得られる非晶質金属ゲートを導入したフィンFETにおいて低周波ノイズを従来技術の約1/5へ低減することに成功した。同技術により、アナログ集積回路の低コスト化につながるチップサイズ縮小と高性能化が期待できるとコメントしている。