Intelの日本法人であるインテルは3月4日、都内で会見を開催し、将来HPC分野で求められるExascaleへの技術の方向性の解説を行った。

|

|

Intel Senior Fellow,chief technology officer for the Intel Architecture GroupのStephen S. Pawlowski氏 |

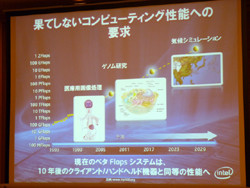

Intel Senior Fellow,chief technology officer for the Intel Architecture GroupのStephen S. Pawlowski氏は、「TOP500で初めて1PFlopsを超えたシステムにIAが用いられて以来、今やTOP500のほとんどが汎用CPUを用いたものとなった。今後、HPCが対応すべき領域はさらに増えていくゲノム創薬には100PFlopsの性能が求められるし、気候シミュレーションには1ExaFlops、そして2030年にはZettascaleの性能が求められることとなる。これを、どう汎用デバイスで実現していくかが、我々の課題となる」とする。

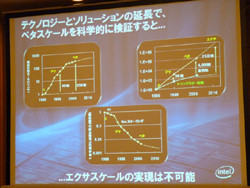

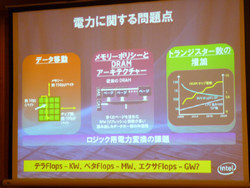

ムーアの法則に代表される半導体技術は、プロセスの微細化によりトランジスタ数を増大させ、その処理能力を増してきた。しかし、同氏は「次の10年はそうしたニーズを維持しつつ、低消費電力性を実現していく時代となる」と説明する。

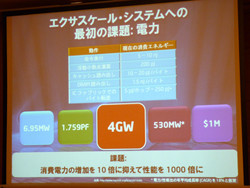

しかし、「今のTOP500の上位システムを拡張して、Excascaleを実現しようとするとその消費電力は4GW必要で、それでは現実的な話にならない」とのことで、性能をおよそ1000倍向上させつつも、あらゆる手段を講じて消費電力の増加は10倍程度に抑えることが可能な「革新的な技術を開発する必要がある」とする。

この消費電力の問題はHPC関連の話では、NVIDIAのChief Scientist & Sr. VP of ResearchであるBill Dally氏 の講演などでも出てきているが、チップ内で演算データを僅かに移動させるだけでも電力を消費する。Pawlowski氏によると、1バイト動かすだけで約10pJ、チップ間でのやり取りになると約100pJのエネルギーが必要となる。

|

|

データをチップ内で動かすだけでも電力は消費される |

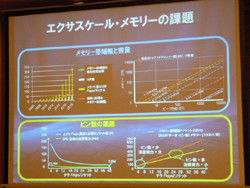

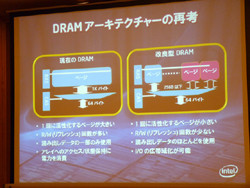

そして、そのエネルギー消費という観点で重要なポイントとなるのがメモリアーキテクチャである。「DRAMアーキテクチャは、大きく変わったところもあるが、バンク部分などはほとんど変化しておらず、電力のロスが大きいほか、トランジスタ数の増加も電力の消費量を増加させる問題となっている」とするほか、処理性能の向上に伴い、従来のDDR/GDDRの延長線上ではメモリの帯域幅が必要とされるレベルと大きく乖離するようになってしまうことを指摘する。

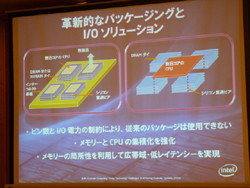

プロセッサ-メモリ間の帯域幅はピン数を増やせば増加させることができるが、それは消費電力の増加も引き起こすこととなり、「専用パッケージを作って対応しようという考えもあるが、それもコストの増加を招く。そうした意味では、標準化された量産可能な技術を用いてコストを抑制させることも必要となる」とし、「HPCやエレクトロニクス業界全体でメモリのヒエラルキの見方を考え直さなければならない。システムアーキテクチャを最適化し、従来のまま使用していくのか、異なる素材などを含めてメモリそのものを変えていくか、どちらかが求められることとなる」とした。

DRAMアーキテクチャを改めて考え直すという意味では、DRAMは1回に活性化するページサイズが大きく、データによってはその一部のみ使用され、残りの部分はエネルギーの無駄となっている場合があるわけで、これをより細かなページサイズとし、必要とされる部分のデータのみを取り出すことで、読み出したデータのほとんどを活用できるようになるとするほか、I/Oの広帯域化もしやすくなるという。

また、「演算をメモリに近づけるでも、メモリを演算に近づけるでもかまわないが」とにかくメモリとCPUの距離を縮めることも重要であり、すでに携帯機器分野で用いられているTSV(シリコン貫通ビア)などの技術をHPCの分野でもコスト的な問題など課題はあるものの、検討していく必要があるとした。

一方のCPU側としても、マルチコア化によるコア間のインタコネクトの方式をどうするか、ということが問題となってくるとしており、こちらについては現在、検討を進めている段階とした。

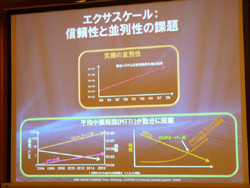

そしてもう1つ、Exascaleのシステムを実現する上で問題となるのが、大規模並列処理の状況下における信頼性の確保だという。「こうした対応は実はまったくと言って良いほど対応が進んでいない」とのことで、今後、そうした課題を解決することも含めて、パラダイムシフトが重要となるという。

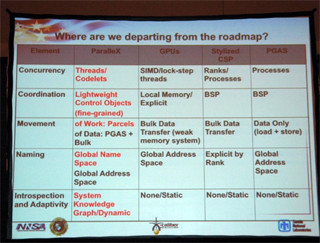

すでにCPUは1スレッドの処理性能からマルチコアでいかに処理性能を向上させるかという流れになっているが、「HPC全体で、自動的に並列処理を実行させる必要がある。これはアプリケーションやコンパイラを実際にどう作らせるかという問題であり、単にCPUやメモリのアーキテクチャを変えるだけでなく、システム全体でシンプルで使い勝手の高い形を維持しながら低消費電力を実現していくかがポイントとなる」とのことで、そうした意味ではハードウェア以上にソフトウェアのあり方が重要になるとする。

「HPCの業界が向かおうとしているのは、アプリケーション側でシステムがどういった構成が良いのかを決めようというもの。ソフト開発者がハード側にこうした機能が必要だと伝えることで、システムそのものの有り様が変わってくる。アルゴリズムの工夫により局所性の向上が可能となる。アプリケーションの最適化をそれぞれ違う構成のシステムで柔軟に行うことができるような方向性を目指す」としており、究極的にはアプリケーションが自身のシステム構成を認識し、最適化を図っていくことが求められるようになるという。「すでにこうしたことを実現するアイデアはいくつも出てきている。しかし、本命といえるものはまだでてきておらず、今後の研究課題となってくる」とした。

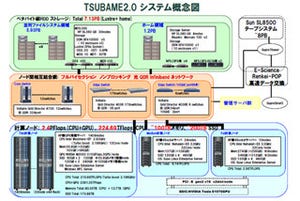

確かに東京工業大学(東工大)のスーパーコンピュータ「TSUBAME」を用いて、青木尊之教授が次世代気象モデル「ASUCA」のGPU化を行った際も、TSUBAMEのハードウェア設計を行った松岡教授にたびたびアドバイスを貰っていたということを語っており、何に用いるかを明確になった時点でハードウェアとソフトウェアが協調して作製していくことが今後の流れになっていくのであろう。

Pawlowski氏は「CPUもGPUも将来の命令レベルでは同様に扱っていきたいと考えている。そうなれば異なるプログラムを用いる必要はなくなる」と語っており、同席したインテルのインテル技術本部 本部長である及川芳雄氏に「ハードウェアが高性能になれば、その上で仮想化した環境を用いてハードウェアを柔軟に用いることができるが、そうした状況であれば、CPUもGPUも区別なく用いることができるようになるのではないか」と聞いてみたところ、すでに仮想化の機能などはあるわけで、将来的にはそうした手法もないわけではないと答えてくれた。