東芝は、不揮発性メモリとして、128Mビット、1.6Gbpsの転送速度を実現したFeRAMを開発したことをISSCC 2009にて2月11日(現地時間)発表する。

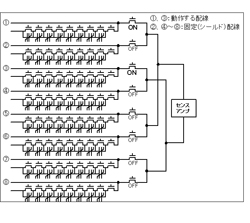

今回開発したFeRAMは、同社独自の「チェーン構造」を改良して用いている。チェーン構造は、プロセスの微細化により増加するノイズを抑制するため(今回のFeRAMには130nmプロセスを採用)、回路内の隣接する2配線を切り替えながら交互に動作させる構造で、同時に動作する配線列が常に1本おきとなる制御方式のため、間に入った固定配線が配線間の干渉ノイズに対する壁となり、微細化が進んでもノイズを減らすことが可能となるほか、省スペース化および集積度向上が可能となる。

今回のFeRAMでは、従来4本で構成していたチェーン構造を8本に改良、これにより、セルサイズの小型化に伴う信号量の低下を防ぐことが可能となり、チップ面積を削減しつつ大容量を実現することが可能となった。

また、デバイスの小型化に伴って、ビット線が短くなることで、読み出し性能およびメモリセルの記憶量(蓄積分極量)が小さくなることから、センスアンプの読み出し信号量が低下してしまうが、チェーン構造により1つのセンスアンプに接続するメモリセルの数を削減し、従来と同等の読み出し性能を維持することに成功している。これにより、全体のセンスアンプの面積は増加するが、改良したチェーン構造により、チップ面積への影響を相殺することに成功した(セルサイズは0.252μm2)ほか、負荷(寄生静電容量)を減少し、読み出しに十分な信号量(200mV)を実現したという。

さらに、データの転送時に電流消費が上がることで起きる内部の電源供給レベルの揺れを予測し、供給電源を細かく調整する電源回路を追加。これにより、データ転送時に必要となる電圧をすばやく上昇させることで、転送速度1.6Gbpsを実現、DDR2インタフェースの搭載に求められる性能を実現した。

なお、同社では、今回開発したFeRAMは、不揮発性メモリでありながら、DRAMと同じインタフェースを搭載しており、システムの性能向上および低消費電力化が可能になるため、今後メインメモリとして携帯電話などの各種モバイル機器や、モバイルPCやSSDなどのキャッシュメモリとしての使用を見込んでいる。