東芝は、NECエレクトロニクスと共同で開発した45nmプロセス技術をもとに、40nm世代のシステムLSI向け低消費電力プラットフォーム技術を開発した。

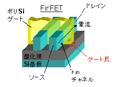

これは、多重フラッシュランプアニール(FLA)の導入と拡散工程における最適な不純物注入、Hf添加絶縁膜の採用を中心としたプラットフォーム技術。FLAを2回行うことで、効率的に不純物を活性化させ、pMOSとnMOSそれぞれの性能向上を実現した。

また、インプランテーションの際に、Geを加えNを導入することで、不純物の拡散領域の拡大を抑制することによりチャネル濃度の上昇を最小限に抑えた。

さらに、ゲート絶縁膜にHf添加絶縁膜を適用、しきい値電圧を上昇させることで、注入される不純物濃度の増大も抑制している。このほか、DFMにより、レイアウト依存性によるトランジスタ性能のバラつき抑制も実現している。

これにより、40nmプロセスでは、65nm世代と比較して消費電力を50%以下に低減することが可能になったほか、SRAM面積0.195μm2を実現した。

同社では、同技術を用いた40nmプロセス世代の製品のサンプル出荷を2008年度第4四半期中に行い、2009年度第2四半期からの量産を計画している。

また、併せて同社は、NECエレクトロニクスと共同で開発した32nmプロセス技術を元に、メタルゲートとHigh-Kゲート絶縁膜を採用することで、45nm世代と比較して、1ロジックゲートあたり50%のコスト削減を実現するプラットフォーム技術を開発した。

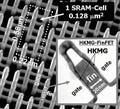

これは、NA=1.3以上の液浸ArF露光装置を用い、照明条件を最適化することで1度の露光で32nm世代の微細パターンを実現する技術。また、メタルゲートとHigh-Kゲート絶縁膜を採用したほか、高解像度露光装置でSRAMセルレイアウトを最適化したことで、SRAMセルのトランジスタのしきい値電圧のバラつき増大の抑制に成功している。

試作されたSRAMのセルサイズは0.124μm2となっている。

なお、同社では、32nmプロセス以降のシステムLSIにおけるコスト競争力の強化に向け、今後も研究を継続していくとしている。