ダイナミック電力を減らすには

ダイナミック電力は、α×(CV2f/2)で表されるので、これを減らすにはfを減らすのが1つの手である。しかし、fを減らすと1秒間で処理できる命令数も比例して減少してしまうので、電力の絶対値は減るが性能/電力は改善されない。その結果、仕事がないときにクロックを落として省エネするには役に立つが、本質的なダイナミック電力の削減にはならない。ということで、残る削減候補はCとVとαである。

まず、Cの削減について考える。これまで使ってきた例では50μmの配線で4つのゲートを駆動し、ゲートはP、Nトランジスタのチャネル幅Wの合計が1μmであったが、これをもっと小さなトランジスタとすること(次の段の遅延時間が長くなる)が出来ればCを減らすことができる。負荷となっている4個のゲート全部が高速である必要がある場合もあるが、その内の1~2個は遅延時間を遅くすることはできないが、残りの2~3個は遅延時間に余裕があるというようなケースも多く、この場合は、遅延時間に余裕がある方のゲートのトランジスタを小さめのものに変えることができる。

また、前述のように隣接した配線がある場合は配線容量が大きいが、隣の配線との距離を大きくできれば配線容量を減らせる。1本の配線の両脇を空けても、その分、別の所が混んで配線容量が増えたりするので、細かく調整するのは難しいが、配線が終わった後に、配線チャネルに余裕がある場合は、図1.18のように配線をずらせて配線の距離が等間隔になるようにして配線容量を減らすという調整を行う自動配線ツールがあり、このようなツールを使うことにより配線のCを減らすことができる。ただし、微細化に伴いレイアウトルールが厳しくなっており、任意の配線ピッチが許容されてない場合は、この手の使用には制約がでる。

そして、配線長が50μmではなくそれより短く配線できれば、配線容量は減る。したがって、各機能ブロックの位置を決めるフロアプランやレイアウトの最適化は配線容量の削減にも効果があるし、良い配線を行って配線長を短縮できる自動配線ツールも重要な要素である。

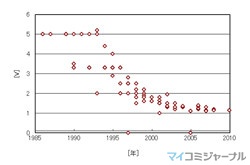

その次の大物の削減候補はVである。Vは2乗になっているので10%削減すると約20%電力が減るということで、他の1乗の項よりも削減の効果が大きい。図1.19にISSCCで発表されたマイクロプロセサの電源電圧の推移を示すが、1990年代の始めから2005年ころまでは、電源電圧を着実に減らしてきている。

CMOS回路のスイッチ速度は、負荷容量Clをトランジスタのドレイン電圧で充放電し、電源電圧VddからVdd/2まで電位を低下、あるいは0VからVdd/2まで電位を上昇させるのに必要な時間である。つまり、負荷容量を一定とするとドレイン電流に逆比例してスイッチ時間が短くなり、高速で動作できるようになる。

なお、トランジスタのチャネル幅に比例してドレイン電流は増加するが、同時にゲート容量(Cgs、Cgd)もチャネル幅に比例して増加する。負荷容量は次段のゲート容量と配線容量の和であるので、着目する(論理)ゲートも、その次段の(論理)ゲートも同じ比率でトランジスタのチャネル幅を増やして大きくしていくと、最終的にはゲート容量に比べて配線容量は無視できる程度の比率となる。

こうなると、さらにトランジスタを大きくしても、ドレイン電流と負荷容量が同じ比率で増加するのでスイッチ速度は速くならない。これが、その半導体プロセスで得られる最高のスイッチ速度である。一方、スイッチ速度は飽和しても、トランジスタサイズを大きくするとそれに比例してゲート容量などが増え、消費電力は増え続けるので、速度と電力のバランスを考えてトランジスタサイズを決定する必要がある。

話が少しそれてしまったが、最近の短チャネルトランジスタでは、飽和ドレイン電流はおおむね(Vdd-Vt)の1.5乗程度に比例する。ここでVddは電源電圧、Vtはトランジスタのスレッショルド電圧である。したがって、Vtを大きくすると飽和ドレイン電流は減り、Vtを小さくすると大きな飽和ドレイン電流が得られる。

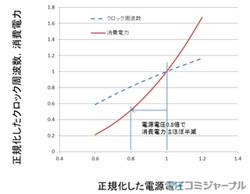

ここで電源電圧Vddを下げると、Vtは一定値であるので、Vdd の低下の1.5乗かそれより急速にドレイン電流が減少する。出力信号のスイッチに必要なVdd/2の電圧変化もVddの減少に比例して小さくなるが、ドレイン電流の減少の方が大きいので、結果としてVddを下げるとスイッチ速度が遅くなり、最大動作クロック周波数が下がってしまう。電源電圧と最大動作クロック周波数と消費電力の関係の例を図1.20に示す。

「コンピュータアーキテクチャの話」が待望の書籍化!

■書籍「コンピュータ設計の基礎」

著者:Hisa Ando

単行本(ソフトカバー:288ページ

定価:2,415円

○本連載「コンピュータアーキテクチャの話」をベースに「実際に設計できる」本当の"基礎"の提供を目指した「コンピュータ設計の基礎」として書籍化されました。コンピュータの基本設計「アーキテクチャ」。その設計を行うエンジニア「アーキテクト」に送る教科書として、実際にコンピュータを設計する場合に役立つ知識を提供する一冊となっています。(編集部)