Texas Instruments(TI)はドイツで開催されていた「Embedded World 2025」に合わせ、米国時間の3月11日にMCU「MSPM0Cシリーズ」を発表した。これに関するオンラインでの説明会が3月18日にあったので、その内容をご紹介したい。

TIは2023年3月にMSPM0シリーズのMCUを発表した。MSPM0シリーズは言ってみれば32bitのエントリー向けという位置づけになり、すでに多数の品種が用意されている(Photo01)が、今回発表されたのはこの中で省メモリ・小型パッケージのM0Cシリーズである。

-

Photo01:一番下段の青いものが今回追加されたSKU。ちなみに製品としては8KB Flashの「MSPM0C1103」と16KB Flashの「MSPM0C1104」の2つが用意される

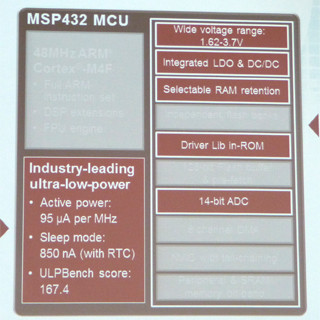

エントリー向けとは言いつつ、内部は割とリッチというか、かなり充実しているのが判る(Photo02)。

-

Photo02:ちなみにProducts Finderを見ると、“5-V-tolerant I/Os, DMA, General purpose, LIN”と書いてあるのだが、LINのI/Fが見当たらない

ただ小型パッケージ品ということもあり、Flash Memoryは8KBないし16KB(SRAMは1KB)だし、Zero-drift OpAmpは搭載されていない。DACとかComparatorもないあたりは、やはりリッチに見えてもエントリー向けということか。

このMSPM0Cシリーズ、ターゲットとなるのはSpace Constrained Device向けということになるだろう(Photo03)。

この手の製品向けの場合、機能を増やすとパッケージも大きくなり消費電力も増えることで、結果として最終製品の大型化とかバッテリー寿命の低下など、価値を損ねる方向に行きかねない。結果、機能・性能とパッケージサイズ・消費電力のバーターになりがちである。なので開発側としては、パッケージサイズを大型化せずになるべく機能を入れてほしい、ということになる。そうしたニーズに対する解の1つが、WCSPの8pinパッケージの追加、という事である(Photo04)。

-

Photo04:ちなみにパッケージオプションは20 TSSOP(6.5mm×5.0mm)、20 VSSOP(5.1mm×4.9mm)、20 WQFN(3mm×3mm)、16 SOT(4.2mm×3.26mm)、8 WSON(2mm×2mm)、8 SOT(2.9mm×2.8mm)、8 DSBGA(1.6mm×0.86mm)の7種類である

WCSP 8ballだと信号ピンが6pinしかないが、逆に6pin分で足りる用途なら本当に胡椒の粒サイズの実装面積で事足りることになるし、もっと信号ピンが必要なら3mm×3mmと一回り大きくはなるが、20pin(信号ピンが18pin)のものもある。用途とか基板の構成にあわせて柔軟に選べる様にした、というものである。特に一番小さなWCSPは、業界最小クラス(Photo05)のパッケージサイズであり、その割にはリッチな機能が搭載されているとする(Photo05)。

-

Photo05:小型パッケージMCUといえば、例えばMicrochipのATtiny202(https://www.microchip.com/en-us/product/attiny202)(8pin SOIC、4.9mm×3.9mm)とかambiqのApollo2 thin(https://ambiq.com/apollo2-thin/)(49pin WLCSP、2.5mm×2.5mm)を思い出すが、これらよりも小さなサイズに収まっている

すでにMSPM0CシリーズのLaunchPadも提供されており、また開発ツールとして従来のCode Composer Studioの他にMSP Zero Code Studioも用意されており、後者はGUI上でDrag & Dropの形でコンポーネントをつないでゆくだけでコード生成が自動で行える、最近流行のノーコード開発環境を提供する。こうしたものを利用する事で、迅速に開発が行える、としている。

-

Photo06:ちなみにMPSM0C1104 Launch Padの価格は5.99ドル。Code Composer StudioおよびZero Code Studioは無償で利用できる。もちろんIARやKeilなどの開発環境も利用できるとのこと

ところで説明後の質疑応答でちょっと気になる事があったのでそちらを。まず従来のMSP430の製品ラインについてだが、もちろん今後も供給するしサポートも提供するが、ただもう新規デザインはMSPM0を推奨しているとの話であった。その意味でMSPM0シリーズはMSP430の置き換え、という位置づけにあるのは間違いなさそうだ。

もう1つ、そのMSPM0シリーズの製造がIn-HouseなのかExternal Fabなのか、またプロセスノードは何か? という話に関して返答が無かったことだ。これはちょっと珍しい話である。ちょっと古い話だが、FRAMを利用するMSP430の場合、そのFRAMの製造を出来るのが同社のダラスにあるDMOS6のみということで、DMOS6で130nmでの製造だった。この頃は、確か長期的には90nmにFRAMを持ってゆく事も考えているといった話があった記憶があるのだが、どうもその話は立ち消えになったらしい。そのDMOS6は2020年にFlashの製造が可能になった(F65)事がPCNから判っている。

同社は2023年11月に行ったプライベートセミナーの中で、必ずしもMCUには先端プロセスを必要としないとした上で、自社FabではアナログやFlashに有利なプロセスを開発してゆくと説明しており、普通に考えれば65nm辺りをつかって現在はDMOS6、将来はこれに加えたLFAB(Micronから2022年に買収したUtah州LehiのFab)でも製造をしてゆくように思えるのだが、今回返答が無かったということは外部のFabを使っている可能性も考慮する必要があるということだ。

TSMCあるいはUMCあたりの40nm~28nm前後なのか、あるいはTSMCの22LLPあたりも可能性としてはあることになる(65nm世代の可能性も残されてはいるが)。どうしてこういう戦略の変化があったのかは不明だが、同社のMCU戦略は色々と変化の時期を迎えているのかもしれない。