今年の「SPIE Advanced Lithography + Patterning学会」(2023年2月26日~3月2日 米カリフォルニア州サンノゼ)は、折しも半導体業界がEUVリソグラフィを用いたスケーリングの継続に向け、パターニング課題の解決につながる新たなブレークスルーを必要としており、高NA EUVの登場でその動きはさらに加速すると見られている時期に開催された。

本稿では特に2つの課題を取り上げ、Applied Materials(AMAT)が同学会で披露した興味深い取り組みについて紹介する。

パターニング課題1:先進的パターニングにおけるコスト、複雑さ、および環境への影響の軽減

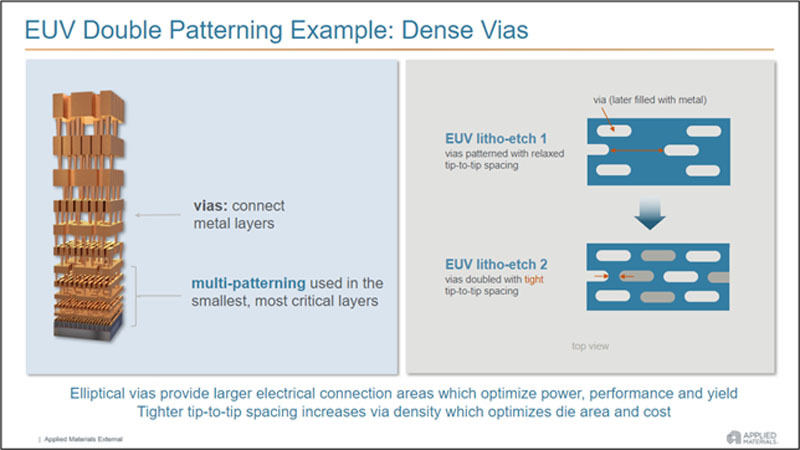

半導体設計者は先進的リソグラフィを極限まで突き詰め、EUVの解像限界を超える細密なパターンを生成して、チップ上により多くのトランジスタやコンタクト、配線を詰め込もうとしている。トランジスタ数が多いほどチップのパフォーマンスは向上し、デバイス上のスペーシングが密になるほどダイの面積とコストを最適化できるからだ。

半導体メーカーはEUVダブルパターニング技術を用いて高密度デザインを2つのマスクパターンに分割し、どちらもEUVのスペーシング限度内に収まるものとする。2つのパターンは中間膜に複写された後、ウェハにエッチングされる。このEUVダブルパターニングはフィーチャー密度を高めるのには有効だが、設計とパターニングが複雑化し、工程数も増えるので、時間、エネルギー、材料、水を多く消費し、ウェハファブとウェハ製造にかかるコストが増大する。さらに2つのマスクパターンの位置合わせエラーが起きるリスクもあり、チップ性能と電力効率の劣化や歩留まり低下につながりかねない。

マテリアルズエンジニアリングを活用してEUVパターンの形を変え、2回目のEUVステップを不要にすると共にスペーシングを狭めて高密度化が可能になるとしたら、業界にとってメリットは大きい。コスト、複雑さ、サイクルタイム、エネルギーと材料の消費などが大幅に改善されるだろう。その方法については、SPIEで論じさせていただいた。

パターニング課題2:EUVと高NA EUVリソグラフィおよびエッチングプロセスの制御

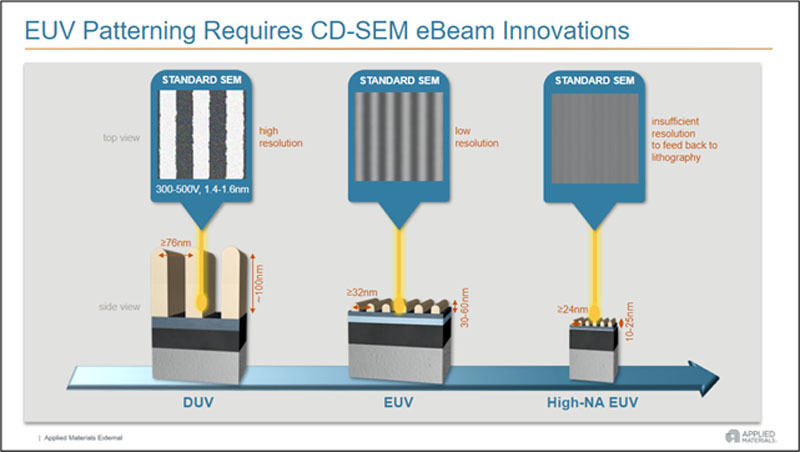

半導体デバイスのフィーチャーを計測するにあたり、CD-SEM(測長走査型電子顕微鏡)装置はしばしば「ファブの定規」と称される。サブナノメートルの精度できわめて正確に計測できるからだ。CD-SEMは、リソグラフィスキャナでマスクからフォトレジストに転写されたパターン上のラインやスペースなどの微細寸法を計測する際に用いられる。得られた計測値はリソグラフィスキャナとプロセスを継続的にキャリブレーションすることで、確実に補正されたパターンがウェハにエッチングされることになる。

このほかCD-SEMは、エッチング後にウェハ上の転写結果と意図されたパターンを照合する際にも用いられる。このようにCD-SEMはエッチングプロセスの制御を助け、リソグラフィとエッチング間のフィードバックループを実現して、高度な照合データセットをエンジニアに提供することで全体的なプロセスチューニングを可能にしている。

EUV、特に高NA EUVの採用によりフォトレジストはさらに薄くなり、デバイスフィーチャーの微細寸法の計測はますます困難になっている。フォトレジストを薄くする必要があるのは、マスクパターンの現像に要するフォトンをDUV(遠紫外線)リソグラフィの10分の1に抑えなければならないからだ。さらに、レジストが薄いほどEUVで形成された高密度ラインの倒壊を防ぎやすくなる。

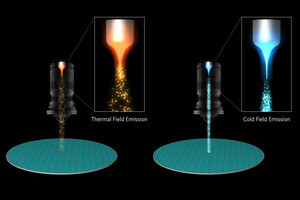

ただし正確な計測値を得るには、高さ30nmほどのフォトレジストのある微小なエリアにCD-SEMで電子ビームを正確に照射する必要がある。さらに、ラインとスペースのピッチがわずか32nmと狭いので、シャープな画像コントラストを得るには電子ビームを細く絞る必要がある。また、電子ビームのエネルギーが強すぎるとフォトレジストと反応して縮みや歪みが生じ、パターンが変化してエラーが出てしまう。

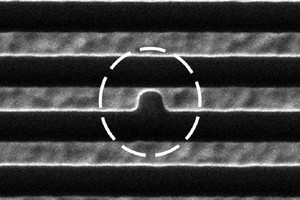

こうした課題は高NA EUVで特に顕著となる。フォトレジストの厚みが最小わずか10nmほどで、ラインとスペースのピッチは24nm程度ないしそれ以下となるからだ(下図参照)。従来のCD-SEMではシャープなコントラストを生む細い電子ビームが作れず、ランディングエネルギーも繊細な高NAフォトレジストの反応を最小限に抑えられるほど低くない。何らかのブレークスルーが登場しない限り、パターニング技術者はリソグラフィとエッチングに手探りで取り組むようなものだ。

SPIEでは、AMATとパートナー各社が高NA EUVへの道を切り開く画期的なCD-SEM技術や技法に関する論文を発表した。さらに、AMATの技術者たちは20件以上の発表を行った。その多くは最先端ロジック、ICAPS、メモリ市場に携わる主要顧客やパートナーとの共同作業に基づいている。

なお、今年のSPIEでは、AMATのカスタマーレセプションが2月27日に開催され、AMATのエグゼクティブやスペシャルゲストがパターニング分野の重要トピックスについて論じている。

本記事は「Applied Materials Blog」を翻訳したものとなります

著者プロフィール

Bala HaranApplied Materials(AMAT)

Vice President of Integrated Materials Solutions