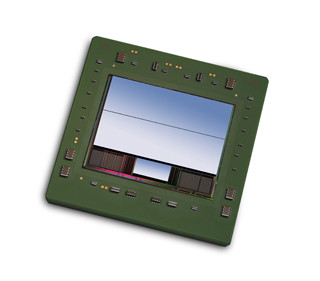

Xilinxは、同社FPGA「Virtex-7」にPCI Express(PCIe) ×8 Gen3準拠のブロックを内蔵し、外付けのDDR3メモリをサポートするソリューションの提供を開始すると発表した。

同製品は、PCI Express Gen3ベースのデザインに必要な全ての構築ブロックを提供するもの。PCI Express Gen3準拠の内蔵ブロックを1866Mbpsの高速メモリインタフェースとともに提供することで、通信やストレージ、サーバアプリケーションなどで求められるシステム帯域幅の厳しい条件を満たすシステムを構築できるという。

競合のメモリソリューションと比較して40%の性能向上を実現する他、中間スピードグレードのデバイスとしては、最大のメモリデータレートを有し、生産性向上に寄与する。また、「Virtex-7 XT」では、SR-IOV(Single-Root I/O Virtualization)機能やマルチファンクション対応エンドポイントを提供するため、データセンターやクラウドコンピューティングなどで求められる新しいニーズに対応できる。

PCI Express Gen3準拠のハードIPコアは、同社のAll Programmableデバイスとして最初の世代となるFPGA「Virtex-7 XT/HT」に搭載して提供される。1866MbpsのDDR3外部メモリインタフェースは、FPGA「Kintex-7/Virtex-7」の両方に搭載され、PCI Expressシステムのスループットをさらに高められる。

また、PCI Express Gen3準拠の内蔵ブロックを使用しないデザインの場合は、ザイリンクス アライアンス プログラムのメンバーであるNorthwest LogicやPLDAからソフトIPコアのサポートが提供されている。

なお、PCI Express用ブロックを搭載するFPGA「Virtex-7 X690T」はすでに提供を開始しており、デザイツール「ISE Design Suite 14.1」での設計が可能となっている。ザイリンクス アライアンス プログラム メンバーのサードパーティ企業から提供されるDMAエンジンおよび1866Mbps DDR3外部メモリインタフェースなど、PCI Express ×8 Gen3ベースのデザインに必要なコンポーネントも全て利用できる。