PSoC 6

さてここから説明はJim Davis氏(Photo04)と中津浜規寛氏(Photo05)に代わり、その新生Cypressが投入するPSoC 6についての説明が行われた。

|

|

|

Photo04:Jim Davis氏(Director, Product Marketing, MCU Business Unit) |

Photo05:中津浜規寛氏(マイコン事業部マーケティング担当シニアマネージャー) |

先の説明にあったが、Cypressはオートモーティブ・IoT・産業機器の3つの分野に焦点を合わせており、PSoC 6はこのうちIoT向けの製品となる。問題はこのIoT向けのマーケットが急速に成長しており、今後はよりパフォーマンスの高い製品が必要となると同社は見込んでいるようだ(Photo06)。

|

|

Photo06:例えばウェアラブル向けで言えば、今後は単に測定データをそのまま表示するのではなく、データのフィルタリングとか集計、あるいはさまざまな機能を搭載することで差別化を図りたいという要望があり、そうした用途にはより高い性能が必要、という判断と思われる |

これに向けて、Cortex-M4コアとCortex-M0+コアのデュアルコア構成にし、さらにBluetoothを搭載したほか、TEE(Trusted Execution Environment)まで内蔵した、ある意味の全部入りがPSoC 6ということになる(Photo07)。そのPSoC 6の特徴は省電力性である。LPモードでは1.1V動作だが、ULPモードでは0.9Vに降圧して動作するため、最大動作周波数は若干落ちるものの、類を見ない省電力性が実現できる、というのが同社の説明だ。RTCと一部のRAM Retention付きのハイバネートモードでは300/600nAという非常に少ない省電力になっているとされる(Photo08)。

|

|

|

Photo07:ちなみに製造プロセスは40nmのULP SONOSプロセスと発表されている。消費電力の少なさは、このULP SONOSプロセスに負うところも少なくないと思われる |

Photo08:ちなみに電圧ドメインは共通なので、例えばCortex-M4コアを1.1V、Cortex-M0+コアは0.9Vといった動作は出来ない(全体で1.1Vないし0.9V)となるそうだ |

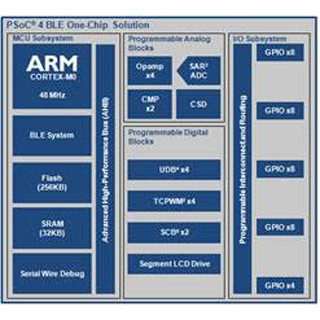

そのPSoC 6の内部ブロック図はこんな感じである(Photo09)。基本的にCortex-M0+コアは通信とかCapSenseの処理などを担う形で、OSの動作などを含むアプリケーション処理はCortex-M4コア側が引き受けるといった形での処理を想定しているという。ちなみにこの図ではTEEあるいはCrypto EngineなどがCortex-M0+側のAux core resourcesとして示されているが、実際には後で図が出てくるがこれらはいずれも共通のMCUサブシステム内に置かれており、なのでCortex-M4側でもTEEの動作は可能とされている。

|

|

Photo09:ちなみに電源投入時にはまずCortex-M0+コアが立ち上がり、次いでCortex-M4側が立ち上がる順序になるという。これもあってか、Cortex-M0+側にはSecBootが用意されている |

そのTEE(Photo10)だが、これは今のところCypress独自のもので、ARMv8MのTrustZoneとは互換性が無い。これに関しては「現時点ではまだセキュリティの標準仕様がそもそも無い」(Davis氏)という話であった。ただ長期的にはARMv8MというかCortex-M23/33を利用したTrustZoneの事も検討してゆく、というやや歯切れの悪い返事であった。なおセキュリティに関しては、暗号化はAESや楕円暗号など複数種類に対応したものがハードウェアで搭載されているとの事だった。

|

|

Photo10:Davis氏によれば、なんでもこのTEEの開発そのものはPSoC 5の頃からCypress社内で行われていたらしい。なのでとりあえずは手持ちのソリューションという形で提供したのだという。なおTEEそのものは128bitで暗号化された状態で実行されるとの事 |

Photo11/12が競合製品との比較である。動作周波数は競合製品と比較して十分高く、そうなるとFlashが追いつかない可能性がある。これをカバーするために8KBの命令キャッシュを搭載しているのも、このクラスの製品としてはちょっと珍しい。またBluetooth 5.0に完全準拠したRFを搭載しているのも特徴で、その割りにGPIOピンが多いのも他との差別化要因ともなっている。もちろんPSoCでお馴染みの「Programmable Analog Block/Digital Block」や、「SCB(Serial Communication Block)」も搭載されている。他に、PSoC Creatorの中からピンの配置を自由に変えられる特徴もそのまま受け継いでおり、例えば開発中にピンの位置に問題があった、なんて場合でもPSoC 6側でそれに対応することでボードのRe-spinをしないで済ませる、なんて事も可能である。

|

|

|

Photo11:MCU Active時の22μA/MHzはULPモードでの数値なので、LPモードだと88μAに上がることになる。ただ競合製品の数値もやはり低消費電力モードでの数字なので、これはこれで正しい比較ではある |

Photo12:こちらは主にBLEモードでの比較 |

また開発キットとしてはArduino Shieldを利用できるBLE Pioneer Kitが用意されるほか、E-inkディスプレイも新たにラインアップされるとの事だ(Photo13)。実際に使ってみるとさすがにE-inkは動作がちょっと遅いが、その分省電力ということもあり、PSoC 6向けとしては適切かもしれない。もちろん既存のArduino ShiledベースのTFTなりセグメントディスプレイなりを使うことも可能だから、別にE-inkのディスプレイが必要という訳ではない。

|

|

|

Photo13:流石に開発キットのロゴはまだ古いままである。このE-inkディスプレイはArduino Shield互換の模様 |

Photo14:動作デモ中。右のCapSenseのスライダを利用してカーソルを移動、ボタンで選択/キャンセル動作となる |

このPSoC 6、量産は2017年第4四半期を予定しており、サンプルは3月14日から順次リリースするとの事だ(Photo15)。

|

|

Photo15:説明時点では、まだEarly Adapt Programのサイトは準備中との話だった。おそらく3月14日の発表と同タイミングでサイトが公開されると思われる |

説明は以上だが、質疑応答を含めてもう少し補足を。まず内部構成だが当初はBT 5.0 RFを搭載したPSoC 63(Photo16)と、BT 5.0を含まないPSoC 62(Photo17)の2つがラインアップされる。良く見るとPSoC 62はBT 5.0の代わりにUSB 2.0を搭載するなど仕様が若干異なっており、なので単純にPSoC 62の上位モデルがPSoC 63という訳ではないようだ。

また現在のラインアップはある意味ハイエンドであり、今後よりメモリ搭載量を下げ、動作周波数を落としたモデルや、Cortex-M0+コアを搭載しないモデルも用意されるという。なので、Photo09ではMain core resourcesとAux core resourcesという形で2つに周辺機器が分かれているが、このAux core resourcesにCortex-M4がアクセスできない訳ではなく、現実問題としては両方のコアからアクセス可能という話だった。

ちなみにCortex-M7に関しては、Davis氏曰く「PSoC 7については、すでに以前に長期ロードマップとしてアナウンスしている」(Photo18)とした上で、具体的なスケジュールなどはまだ言えないとした。さらに自動車向けのFMシリーズとの統合については「次世代の製品は両方を統合していく事になると思う」という話であった。

|

|

Photo18:出典はCypress Product Roadmap。まだPSoC 7はコンセプトの段階である。 |