2016年6月には、理化学研究所(理研)のスーパーコンピュータ(スパコン)「菖蒲」でGreen500で1位、TOP500でも94位とTop100入りを果たして注目を集めたPEZYグループであるが、2016年11月のTOP500では新システムの登録は無く、Green500でもNVIDIAのP100 GPUを用いるシステムに抜かれて3位に後退した。沈黙を守るPEZYグループは、今、何を進めているのであろうか?

|

|

PEZYの石川氏 (写真は2016年6月に理研で開催された発表の際に筆者が撮影したもの) |

2016年12月に東京大学(東大)で自動チューニングに関するシンポジウムが開催され、そこで、PEZYの石川仁氏が招待講演を行った。自動チューニングのシンポジウムであるので、プログラミング関係の話が中心であるが、その発表の中に、PEZYが今、何をやっているのかについて、いくつかのヒントになる情報が発表された。同講演の内容をもとに、その動きを読み解いてみたい。

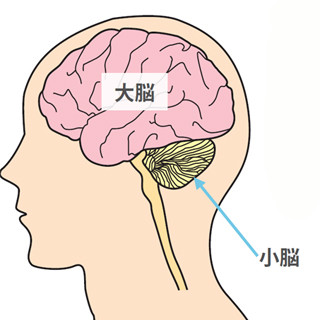

ちなみにPEZYグループであるが、メニーコアのプロセサを開発するPEZY Computing、液浸の冷却を含めHPCシステムを開発するExaScaler、超広帯域の3D積層メモリを開発するUltraMemoryの3社からなる。しかし、3社を合わせても80人に満たないスパコン開発としては小さな所帯である。

|

|

PEZYグループは、メニーコアプロセサを開発するPEZY、HPCシステムを開発するExaScaler、3D積層DRAMを開発するUltraMemoryの3つの会社で構成されている (以下の図は、石川氏の発表スライドのコピーである) |

PEZYグループのスパコンの現状

現在のPEZYは、以下の6台のスパコンを開発し、稼働させている。「睡蓮」と「青睡蓮」は高エネルギー加速器研究機構(KEK)、「菖蒲」、「紫陽花」、「皐月」は理研にそれぞれ設置されており、「さくら」はPEZYの社内に設置されている。

PEZY-SCはTSMCの28nmプロセスで製造される1024コアのメニーコアプロセサである。クロックは733MHzで、単精度浮動小数点演算のピーク性能は3TFlops、倍精度の場合は1.5TFlopsである。NVIDIAのP100のように16nmプロセスを使うGPUと比較すると演算性能は見劣りするが、28nmプロセスのチップとしてはトップレベルの演算性能を持っている。そして、消費電力は70WとハイエンドGPUと比べてかなり小さい。これが2016年6月の菖蒲スパコンのGreen500の1位の獲得に効いている。

次の図の右側上の写真がブリックという構成単位で、白っぽいヒートシンクがXeonプロセサ、両側の4個の黒いヒートシンクがPEZY-SCである。ブリックには、このノードボードが4枚含まれている。そして、ZettaScaler-1.6システムでは16本のブリックを1つの液浸槽に収容している。冷媒は高沸点のフロリナートを使い、気化熱は利用していない。右下の写真に見られるように、菖蒲ではこの液浸槽を5台使用している。

研究者にとっては、PEZY-SCベースのスパコンには興味はあっても、自分が使えなければ、絵に描いた餅である。一方、PEZYにとっては、利用者をリクルートし、将来の顧客を獲得することが重要である。このため、共同開発という形で、これらのスパコンを利用してもらうという努力を行っているという。

次の図のように、使いたい人から実装に必要な情報を提供してもらい、PEZY側で可能な範囲で評価を行うという。積層DRAMを開発するUltraMemoryを別にすると、40人弱の所帯であり、その半分がソフトウェアエンジニアとしても20人程度であるので、多くのポテンシャルユーザが殺到すると手が回らないという事態は充分予想される。

利用のパターンとしては、空冷の2ノードシステムを購入してもらう、あるいは理研の菖蒲スパコンの利用公募に応募して、菖蒲の時間を確保するという方法があるという。

PEZYグループの次世代スパコンの開発

2016年11月には、PEZYグループからのTOP500やGreen500への新しい登録は無く、今後、どうしていくのかであるが、まず、2048コアとコア数を倍増した「PEZY-SC2」を開発する。PEZY-SC2では、UltraMemoryが開発する3D積層DRAMを接続して、メモリ帯域を拡大する。発表では言及が無かったが、TSMCの16nm FinFETプロセスを使っているようである。そうすると、コア数倍増に加えてクロック周波数の向上が期待され、発表時には1GHzという値も示された。クロックが1GHzとなるとピーク演算性能は4TFlopsを超え、NVIDIAのP100の4.733TFlops(Base clock 1328MHz時)には及ばないが、性能/電力では超えられる可能性がある。これにUltraMemoryが開発中の3D積層メモリを加えると、さらに性能アップとメモリ部分の消費電力低減も予想される。そして、液浸冷却システムも改良して冷却効率を改善したZettaScaler-2.Xシリーズを開発するという。

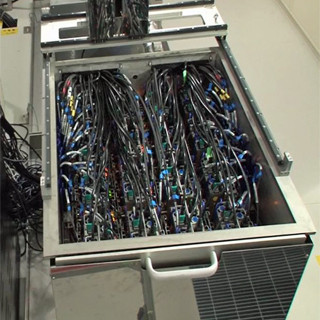

この石川氏の講演では言及が無かったが、2016年11月のSC16の展示では、PEZY/ExaScalerは、液浸槽には380V DCを供給し、そこで48V DCに落としてPEZY-SCノードに供給するという高電圧DC給電システムを展示していた。次の図は48V DC給電のPEZY-SCノードの写真で、右側の2つ灰色の箱がDC48VからPEZY-SCに供給する1V以下の電圧を作るDC-DCコンバータである。

PEZY-SC2の電源電流は100Aを超えると考えられ、48V給電でIRドロップによるムダな電力消費を減らそうという作戦である。これもPEZY-SCからSC2へのアップグレードに上積みされる。

そして、PEZY-SC2には、PEZY-SCのARM962コアに変えてより性能の高いMIPSコアを集積する。このMIPSコアはPEZY-SC2コア群と同じメモリを共用するので、MIPS CPUからPEZY-SC2へのデータ転送は必要が無くなり、性能の向上、消費エネルギーの低減が可能になる。

ただし、PEZY-SC2ノード間のデータ通信は無くならないので、MPSコアとPEZY-SC2がメモリを共有することが、全体としてどの程度の性能向上につながるのかは、ハードウェアとして何ができるのかと、InfiniBand NICのようなインタコネクトをどのように制御するのかに影響される。

日本の次世代スパコンプロセサの開発としては、富士通のポスト京向けのARMプロセサ、NECのAuroraプロセサとこのPEZYのSC2がある。しかし、富士通のポスト京は2020年以降と見られ、かなり先である。NECのAuroraも2018年の製品化である。

これに対して、PEZY-SC2はテープアウト間近であり、2017年11月のTOP500やGreen500に性能値を提出することを目指しているという。少なくとも2017年の国産スパコンはPEZYに注目ということになりそうである。