さまざまな新規技術を使い分け

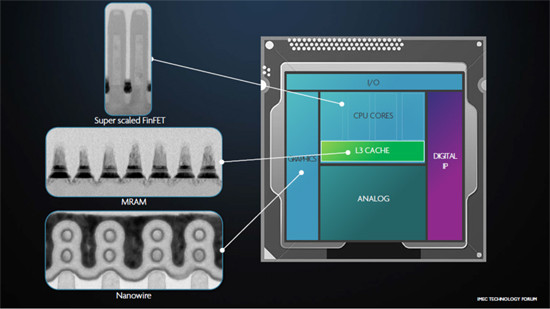

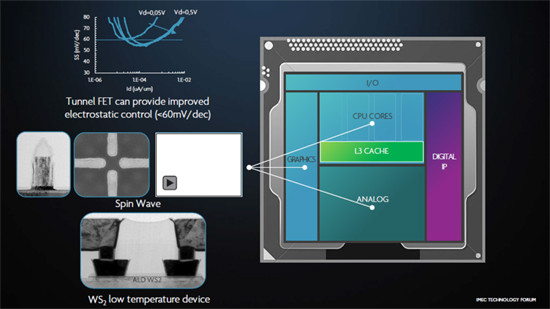

図1の右が典型的なSoCのブロックダイアグラムを示したものだ。SoCは心臓部にCPUコア(キャッシュメモリを含む)、高速画像処理のためのグラフィックス回路、I/O回路、その他のデジタル回路やアナログ回路で構成されている。今までは1種類のトランジスタ技術やプロセスで多くの回路が構成されてきたが、3nm以降は、それぞれブロックごとに、さまざまな新規技術から最適のモノを選択することになるだろう。

例えば、図1左にあるように、性能とコストを考慮して、CPUコア部には、超微細化FinFET、キャッシュメモリにはMRAM(磁気抵抗変化型メモリ)、グラフィックス回路はナノワイヤFETという具合である。トンネルFET、スピン波FET、WS2(二硫化タングステン)といった新規技術が実用段階になれば、これらに置き換わる可能性もある。

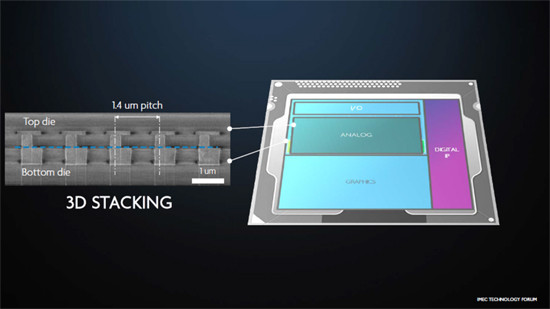

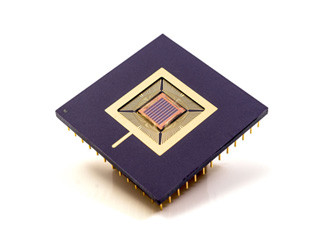

また、チップの一部あるいは全部を3D積層することもありうるだろう(図3)。

imecでは、AIチップや量子コンピュータチップなどもすでに開発を進めており、非ノイマン型コンピューティング時代の到来にも備えているという。

次世代メモリはどれが主流になるのか?

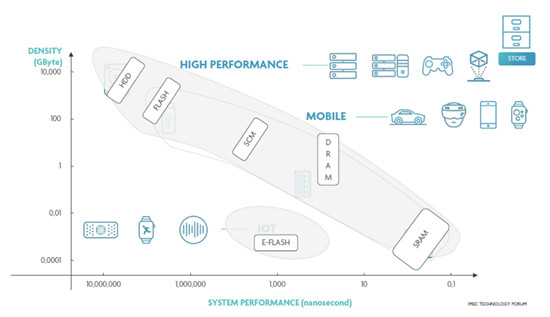

最後に、次世代メモリについて展望したい。その前に、半導体メモリの現状について考察しておく必要がある。図4は、既存のメモリ/ストレージの記憶容量(GByte) とシステム性能(読み書き速度:ns)の関係を示したものだ。

記憶容量は最も大きいが速度の遅いHDDや、HDDよりは速度がやや速いフラッシュメモリ、対照的に記憶容量は小さいが超高速でキャッシュメモリとして活用されているSRAM、その中間にDRAMや最近登場しつつあるストレージクラスメモリ(SCM)があるという具合である。それに、今後は、さまざまな次世代メモリが実用化されるに至り、既存メモリともども守備領域をさらに広げていくことになることが予想されている。

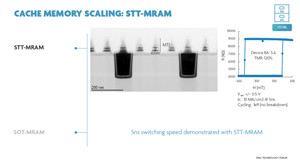

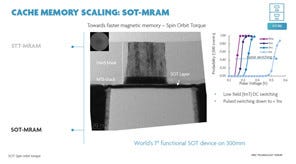

新しいメモリアーキテクチャは、いまだ研究段階にあるものが多い。「今のところMRAMが、SRAMキャッシュやDRAMの代替品として最も見込みがある」とSteegen氏は語るが、MRAMを5nm以下に適用しようとすれば、新たなトランジスタ構造が必要になるとみられる。現在、imecでも、キャッシュメモリ用途にSTT(Spin Transfer Torque)-MRAM(スピン注入磁化反転方式型磁気抵抗変化型メモリ)と、さらに高速なSOT(Spin Orbital Torque)-MRAM(スピン軌道トルク磁化反転方式型磁気抵抗変化型メモリ)の研究を行っているというが、DRAM代替としてはSTT-MRAMとFeRAM(強誘電体メモリ)が候補に挙がっているとする。

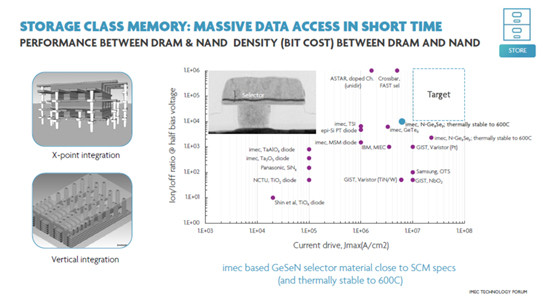

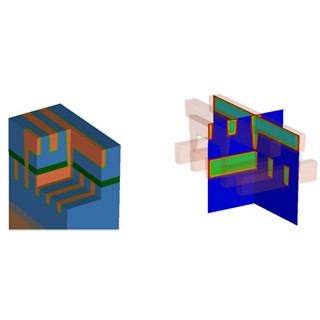

Streegen氏によると、半導体業界はストレージクラスメモリ(SCM)の候補として、少なくとも5つの技術を開発中だが、そのほとんどがクロスバーメモリや抵抗可変型メモリの変型だという。クロスバー部分の記憶材料としては図8に示すようにさまざまな材料が提案・検討されているものの、imecでは、600℃まで熱的に安定なGeSeNを本命視して研究しているとする。ただし、まだ、仕様(オン電流とオフ電流の比率および駆動電流)が目標(図8の点線で囲んだ枠内)には達していない。

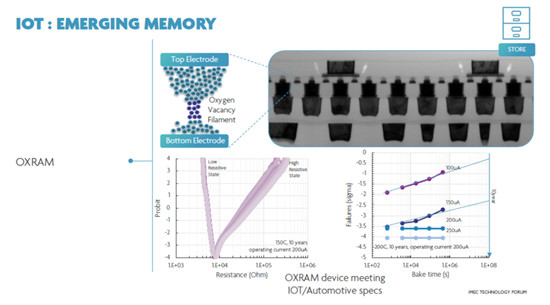

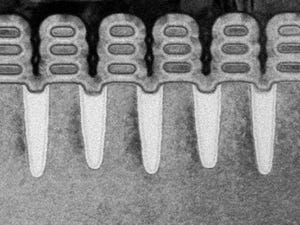

このほか、imecは、遷移金属酸化物の酸素空孔を利用した抵抗可変型RAMであるOxRAM(Oxide-based RAM)(図9)をIoT端末用のeFlash(組み込みフラッシュ)代替に活用する方向で検討している。AI(人工知能)チップの一種である自己学習型ニューロモルフィックチップ(神経形態学的半導体デバイス)のメモリ機能部にすでに使用しており、マシンラーニングに活用している。OxRAMは、高温動作が可能なので車載用途に活用することも考えているようだ。

なお、imecでは次世代の実装技術にも注力している。新しいパッケージング技術であるファンアウト・ウェハレベルパッケージング(FOWLP)や超高速デバイス向けにマルチコアファイバー光配線とシリコンフォトニクスチップとの実装技術(図11)についても研究しているという。