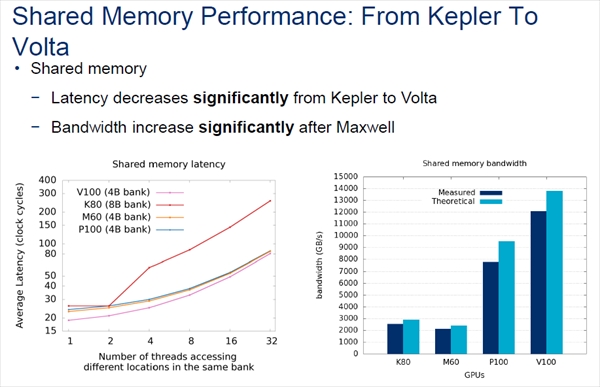

レーテンシ、バンド幅ともに改善したシェアードメモリ

次の図の左側のグラフは、シェアードメモリのレーテンシの測定結果を示している。横軸は、同じバンクの異なるアドレスをアクセスするスレッド数で、これが増加するとバンクコンフリクトが増えてレーテンシが増加する。

特にレーテンシの増加が大きいのは、Keplerで競合スレッド数が2から4に増えるところでレーテンシが急増している。MaxwellとPascalは、ほぼ同じ特性で、競合スレッド数が大きい部分ではKeplerから大きくレーテンシが改善している。そして、VoltaはPascalに比べて競合スレッド数が少ない領域でレーテンシが減少している。

右側のグラフはシェアードメモリのバンド幅の測定結果で、K80、M60、P100とV100を比較している。2本の棒グラフは左が実測、右は理論的ピークバンド幅である。PascalはMaxwellに比べてバンド幅が4倍近く増加しており、Voltaではさらにバンド幅が増加して12TB/sという値が測定されている。

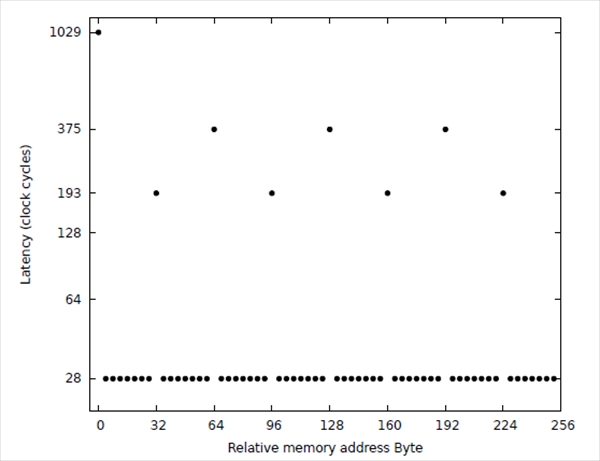

グローバルメモリのアクセスレーテンシ

次の図は、arXivの論文に載っているグローバルメモリをアドレス順にアクセスした場合のレーテンシを示すものである。28サイクルでアクセスされている部分はL1データキャッシュをヒットした場合で、この値はL1データキャッシュのレーテンシである。193サイクルのレーテンシはL1データキャッシュをミスしてL2キャッシュにヒットした場合のレーテンシである。

375サイクルになっているのは、L2キャッシュをミスしてデバイスメモリをアクセスした場合のレーテンシである。そして最初の1029サイクルのレーテンシになっているのは、さらにTLBをミスして、デバイスメモリに格納されたページテーブルをアクセスすることが必要になった場合である。

Voltaではそれ以前の世代のGPUと比べて、キャッシュのアクセスレーテンシは短縮されているのであるが、それでもCPUのキャッシュに比べるとL1、L2キャッシュのレーテンシは1桁遅い。

-

アドレスを順に変えてメモリをアクセスした場合のレーテンシ。28サイクルのL1データキャッシュがヒットした場合である。L1データキャッシュをミスしてL2キャッシュにヒットした場合は193サイクル、L2キャッシュをミスしてデバイスメモリをアクセスした場合は375サイクルとなっている。1029サイクルを必要とした最初のアクセスは、これにTLBミスが加わっている

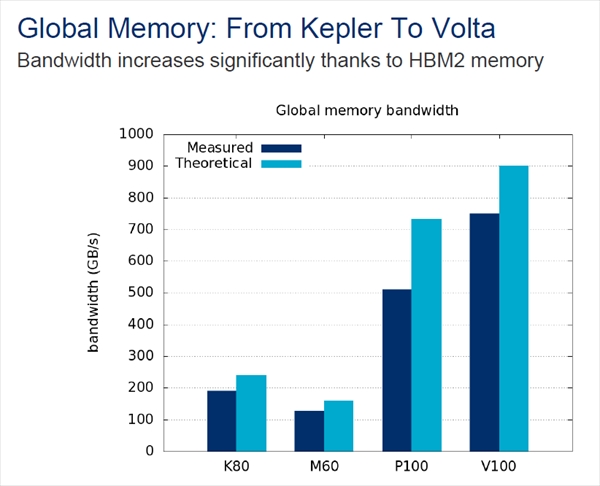

デバイスメモリのバンド幅

次の図は、GPUチップ外に置かれたデバイスメモリのバンド幅を比べたものである。P100とV100では3D積層型のHBM2 メモリを使っており、P100の実測では510GB/s、V100の実測では750GB/sという高い実測メモリバンド幅が得られている。

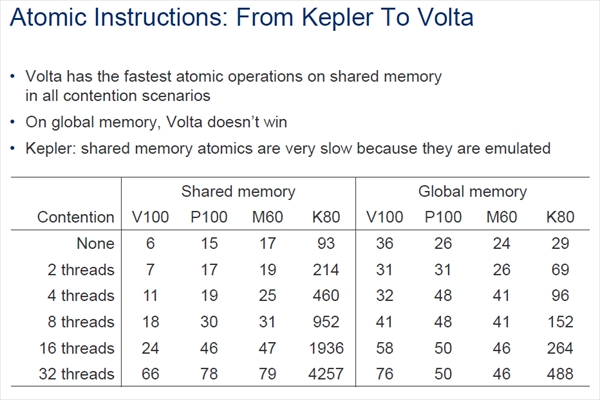

シェアードメモリを使うアトミックアクセスの性能が向上

次の図はアトミック命令の実行レーテンシを示す表で、左側はアトミックアクセスの対象がシェアードメモリの場合、右側はグローバルメモリの場合である。そして、一番上の行は、同じメモリをアクセスするスレッドが1つの場合、次の行は2スレッドが競合する場合、順に、4スレッド、8スレッド、16スレッド、32スレッドが競合する場合のレーテンシを示している。

シェアードメモリを使った場合は、Voltaのレーテンシは過去のGPUのどれよりも短いレーテンシとなっている。一方、グローバルメモリを使う場合は、Voltaのレーテンシは過去のGPU世代と比べて短縮されているという訳でもない。

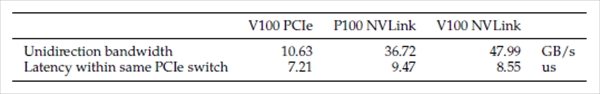

GPU同士、CPU-GPUの通信

次の図の上側の表は、GPU同士の通信バンド幅とレーテンシを示す。なお、バンド幅は一方向のバンド幅で、逆方向もほぼ同じバンド幅で、同時に通信を行うことができる。

PCIeを使うPCIe版のV100では10.63GB/sの通信バンド幅であるが、NVLinkを使うGPUでは大幅にバンド幅が向上している。特にNVlink2を使うV100 NVlinkでは48GB/sとPCIe版の4.5倍のバンド幅となっている。

一方、レーテンシは7.2μs~9.5μsで、どの構成でも大差ない。

下側の表は、ホストCPUとGPUの間の通信バンド幅を測定した結果である。NVLink接続を持つPower CPUは使っていないので、すべての測定でCPUとの接続はPCIeであり、バンド幅も同じとなっている。

-

GPU間の通信のバンド幅とレーテンシ。PCIe版V100では10.63GB/sのバンド幅であるが、NVLink接続のP100では36.72GB/s、NVLink2のP100では47.99GB/sと大幅にバンド幅が増えている。GPU世代や通信路の違いがあるがレーテンシは大差ない値である

最後に、GPU世代を通して変わっていない項目をまとめる。

- L2キャッシュはユニファイドキャッシュで、データ、定数、命令で共有

- TLBを持ち、L1キャッシュは仮想アドレスで索引され、L2キャッシュは実アドレスで索引される

- 定数のキャッシュは、3レベルになっている

- 命令キャッシュも3レベルになっている

なお、この論文の情報は、NVIDIAの公表した情報ではないのですべて正しいという保証はないが、マイクロベンチマークを作って実測しているので、概ね正しいと思われる。また、Tensorコアの動きはNVIDIAのバイナリをディスアセンブルするような方法で確認しており、正しいものと思われる。

NVIDIAから、ここまで詳しい情報が公開されるとは考えにくく、貴重な情報である。この情報を公表してくれたCitadel Securitiesの著者たちに感謝したい。