NECエレクトロニクスは19日(米国時間)、45nmおよび40nmプロセスにおいて、しきい値電圧の不規則なばらつきを低減する技術を開発したと発表した。同技術は、電源電圧に占めるしきい値電圧の割り合いの高いSRAMの開発において特に有効という。

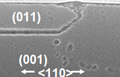

同技術の発表は、米国ホノルルで開催中の「2008 Symposium on VLSI Technology」にて行われた。同技術はゲート絶縁膜にハフニウム(Hf)を用いることにより、ゲート電極とSi基板の間に生じる電位差(仕事関数)を制御し、チャネルに含まれる不純物濃度を低減するもの。

チャネル中に不純物を導入するイオン注入工程において、注入するイオンの量(不純物の量)は不規則にばらつく。このばらつきはしきい値電圧にそのまま影響する。また、このばらつきはプロセスが微細化するほど、不純物の量が多いほど大きくなる。同技術では、この不純物の量を低減することにより、ばらつきを低減している。

同社では55nmプロセスにおいて同様の技術を開発しているが、同技術ではさらに45nmおよび40nmプロセス向けにチャネル構造を最適化している。同技術を用いてSRAMを試作した結果、しきい値電圧のばらつきを従来比で18%低減できたという。

発表によると、同技術をSRAMに採用すれば動作アシスト回路が不要になるうえに、動作電圧や電流などについてのマージンが確保できるという。また歩留まりが改善し、製造コストが低くなる可能性もある。