Gen3

さて、今回の本命はGen3である。Gen3の基本的なターゲットは8GT/sでの転送である。基本的な話は以前レポートしたが、まず大きな違いは最終的に128b/130bのエンコーディングを使うようになったことだ。詳しくは次のレポートで書くが、やはりScramblingだけでは無理だった様だ。

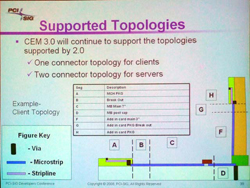

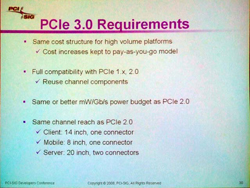

それはともかく、Gen3はPHY以外は極力変えない、というのが現在のスタンスであることに変わりは無いようだ。既存のGen1/Gen2のコンポーネントや配線に関しては、そのままGen3に移行できる様に配慮しているとのこと。現在はまだシミュレーションの段階だが、シミュレーションモデルは従来と同じ1 Connectorのものを使っているとの説明だった。

|

|

|

Gen2よりも「転送速度あたりの消費電力を下げる」というのが目標だそうだが、転送速度そのものはあがるから、絶対的な消費電力そのものはあがるかもしれない |

一番クリティカルなのは、バックプレーンなどで使われる2 Connectorのパターンで、こちらは流石にそのままでは行かない模様。詳しくは後述 |

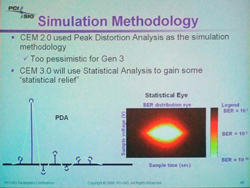

現時点ではまだScramblingに関する方式がちゃんと決まっていない模様で、これの影響とかマージンのとり方、より低価格なイコライザの方式などが今後の課題とされている。

ちなみに互換性に関して言えば、ベースとなるのはGen2となるため、少なくともGen2との互換性は必ず保つことが必須とされる。「将来、つまりGen4とかその先になれば、Gen2以下との互換性を持たなくなる可能性はあるが、Gen3に関してはGen2以下との互換性は必須」との事で、Gen3ではGen1/2互換PHYとGen3 PHYの両方を搭載するのは必須になるようだ。

|

|

|

基本的にはGen3のターゲットは65nm/45nmプロセスであり、このクラスであれば性能的には問題ないし、ダイサイズが肥大化してもそれほど影響はないだろう、との見解であった |

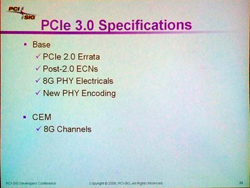

PCIe 2.0をベースにErrataやECNを取り込み、さらにGen3のPHYのスペックを追加したものがPCIe 3.0 Base Specificationとなるとのこと。GEMはGen3用のものが新規に作られる模様だ |

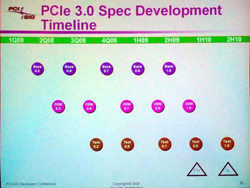

そのGen3、現在の予定では2009年後半にはBase Specification 1.0をリリースしたいとのこと。ただ、CEMはそこから1四半期遅れになるし、Test Specificationは9カ月遅れとなる。「通常Test Specificationは9カ月ほど時間差がある。実際に製品を動かして、そこからのフィードバックを集める期間が必要だからだ」という話で、したがって実際に製品が出荷開始状態になるのは2010年に入ってから、というのが現在の見込みだ。ただメーカー自身は「Base Specが0.9の頃には、通常サンプルは出てくるのが普通だ」ということで、チップセットベンダなどからテスト用シリコンがOEMベンダに出回るのは、早いと2009年前半になるかもしれないとのことだった。

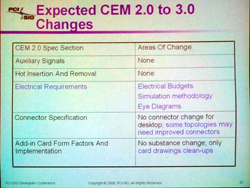

ちなみにCEMに関しては、基本的にはCEM 2.0とほとんど違いが無いが、Electrical Requirementに関してはより厳しくなるのは半ば必然的であり、さらにメザニンコネクタに関しては多少変更が必要になりそうだ、との事。やはり8GT/sの複数層配線はきついようだ。最後に簡単なシミュレーション結果も示され、今のところは8GT/sがうまく動作するであろうという見通しが示された