IntelコーポレートプラニンググループのシニアバイスプレジデントであるStuart Pann氏は8月19日(米国時間)、「ファウンドリパートナーシップの拡大」と題する文書を公開した。

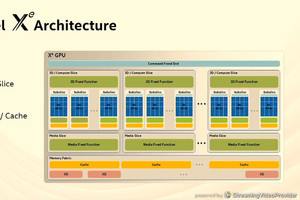

先般開催されたIntel Architecture Dayで発表されたGPUであるXe HPCマイクロアーキテクチャに基づく新しいゲーミングディスクリートSoC「Intel Arc」ならびに「Ponte Vecchio」をTSMCの「6nmプロセス(TSMCの表記ではN6)」および「5nmプロセス(N5)」を用いた製造委託を行うことに決めた背景についての説明だという。

Intelがファウンドリに製造委託する理由

新しく結成されたコーポレートプラニンググループのリーダーとして外部のファウンドリパートナーとの関係を管理する責任を負うPann氏は、「なぜIntelは社内に製造工場がいくつもあるにもかかわらずファウンドリに製造委託するのか」という質問を投資家はじめ多くの外部の人から再三浴びせられているという。

これに対して同氏は、「Intelは過去、何十年にもわたって外部ファウンドリを使ってきた。現在も製品全体の20%を外部ファウンドリに製造委託しており、IntelはTSMCの上位顧客の1社である。Intelの歴史的に、Wi-Fiモジュールやチップセットなどのコンポーネントのほか、イーサネットコントローラなどを外部ファウンドリに製造委託することで、社内の最先端テクノロジーとの補完関係を構築してきた」といままでもファウンドリを使ってきたことを強調しているほか、今後について、「3月に発表されたIntelのIDM 2.0戦略の一環として IDMモデルの進化形として、主要なファウンドリとのパートナーシップをさらに深め、拡大していく。これらのXe製品は、そうした進化の最初の製品であり、ファウンドリの最先端ノードを初めて利用することになる。その理由は単純で、設計者が適切なワークロードに適切なアーキテクチャを使用するのと同じように、そのアーキテクチャに最適な技術ノードを選択したということである。現時点では、TSMCの最先端技術ノードを選択することはIntelのディスクリートグラフィックス製品にとって正しい選択である」と述べている。

差別化は独自のパッケージング技術

しかし、Pann氏は、すべてをファウンドリに任せてしまうわけではなく、「次の進化は、アーキテクチャへのモジュラーアプローチによって推進される。つまり、さまざまなプロセスノードでシリコンチップレット(タイル)を個別に製造し、高度なパッケージング技術を介してそれらを接続して製品を完成させる。これにより、多くの半導体製品がSoCからシステム・オン・パッケージ(SoP)技術に移行する。SoPはすでに具体化されており、クライアントコンピューティング向けCPU「Meteor Lake」などで本格的に使われるようになる。Meteor Lakeの主要チップレット(タイル)は、 最先端となるIntel 4プロセス(Intel 7nmプロセスのEUVリソグラフィ採用による歩留まり改善版) を使用して製造されるほか、一部のサポートタイルがTSMCで製造される」と、Intel独自のパッケージングで差別化を図ることも強調している。

外部ファウンドリ連携の背後に見える供給量の早期確保

なお、今回のTSMCとの提携強化の正当性については、「過去1年間で、PCセクターの需要が急増しており、この高い需要は今後数年間は続くと予想される。この長期的な需要を満たすために新工場に対する投資計画はすでに公表しているが、新しい最先端ファブで製造を開始するまでには時間がかかる。IDM 2.0モデルのユニークな利点は、利用可能なすべてのツールを活用して、顧客への短期的な供給を確保できることである。また、これにより幅広いプロセステクノロジーの選択が可能となり、モジュラーアプローチ、社内の工場ネットワーク、およびファウンドリとの親密なパートナーシップの組み合わせが競争上の優位性を発揮することとなる。」と述べている。