東京工業大学(東工大)ならびに科学技術振興機構(JST)は、IoTの進展において求められている小型かつ省電力性能を備えた新型プロセッサ「SubRISC+」を設計、LSIとして集積したことを発表した。

同成果は、東工大のMingyu Yang大学院生、同・工学院 情報通信系の原祐子准教授らの研究チームによるもの。詳細は、米国の科学誌「IEEE Access」に掲載された。

IoTの発展に伴って多種多様なデバイスやセンサが活用されるようになってきたが、今後はさらにその数が増えていくことが予想されている。世の中が便利になる一方で、その実現においては、デバイスやセンサとデータセンターやサーバなどとの間をつなぐネットワークのトラフィックの増大が懸念されている。

そこで現場、いわゆるエッジのコンピュータ(エッジコンピューティング)がある程度の処理を行い、必要があればクラウドにデータを送ることで、ネットワークの負荷を軽減すること、ならびにリアルタイムで処理することで遅延の低減といったことが期待されている。

しかし、エッジコンピューティングもまた、既存の組み込みシステム向けのプロセッサでも必要とする消費電力はまだ大きく、エッジコンピューティングに採用するには適していないということから、より低消費電力かつ高性能なプロセッサが求められている。

そうした中、研究チームが小型のエッジ端末用プロセッサを開発するにあたって着目したのが、近年の組み込みシステム向けプロセッサが、小型のエッジ端末に用いるにしてはオーバースペックであるという点だった。

-

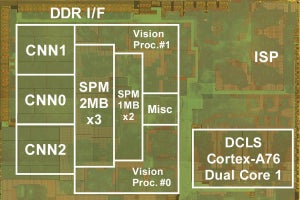

小型マイクロプロセッサの比較表。(左)今回のSubRISC+。(中央)商用プロセッサで最も小型なARM製Cortex-M0。(右)スイス・チューリッヒ工科大学で開発された「RISC-V Micro-riscy」 (共同プレスリリースPDFの表を下に作成)

近年の組み込みシステム向けプロセッサは、アプリケーションの多様化に伴って命令数が増え、小規模なものであっても約50種ほどの命令を扱っている。例えば商用の最小32ビット組み込みプロセッサとされるArm Cortex-M0でも命令数は約60となっている。その結果、回路面積や消費電力が要求に対し上回る傾向にあった。

そこで研究チームは今回、小型エッジ端末で必要な計算を実用的な時間で処理するための機能に限定させることで、回路面積を削減し、小型化と省電力化を両立するLSIを開発することに成功したという。

このプロセッサは、減算・シフト・論理演算・メモリアクセスの4種類の命令のみで構成されるRISCプロセッサで、減算結果に応じて条件分岐するという特徴を持つことから、このアーキテクチャは「SubRISC+」と命名された。

ちなみに近年は、心電図・加速度などのデータのセンシング機能が、ウェアラブルデバイスや携帯端末に搭載されることが増えている。SubRISC+は、それらのデータから異常検出やデータ探索する軽量アルゴリズムをリアルタイムに処理し、警告などの限られたデータのみを送信する用途を想定して開発された。また、SubRISC+は「チューリング完全」であるため、これらの用途以外のあらゆるプログラムを処理することも可能としている。

また今回の研究ではソフトウェアの一例として、加速度データからてんかんの発作をリアルタイムに検出可能な軽量アルゴリズムを実装し、実用性を実証したという。動作周波数を50MHzと想定したシミュレーションでは、データのサンプリング速度より高速に異常検出でき、なおかつ131.1μWという電力であったとした。さらに、Cortex-M0で同じ処理を行い、比較を行った結果、SubRISC+の方が1.4倍高速で、なおかつ電力効率は2.7倍、エネルギー効率は3.8倍であることが確認されたという。

なおSubRISC+のLSIはデータメモリを4KB、命令メモリを2KBとして設計。65nmプロセスで製造され、ダイサイズは1mm×1mmとしている。

このLSIを5MHz(ヘルスケアの異常検出ではリアルタイム処理を十分確保できる周波数)で駆動した場合の消費電力は77.0μWであり、ボタン電池(LR44)で駆動させた場合、約100日連続稼働できる試算であるという。

研究チームは、今回開発されたSubRISC+試作チップの性能が確認されたことから、今後はプロトタイプのサンプル配布や展示会への出展を検討中だという。それに加え、IoTセキュリティ向けにSubRISC+プロセッサをさらに拡張し、より幅広い応用展開を可能にするチップの試作と実用化も目指すとしている。