Hot Chips 29において、Xilinxは3次元積層メモリ「HBM2」を搭載し、高速のアクセラレータ接続インタフェースであるCCIXをサポートするFPGA「UltraScale+」を発表した。

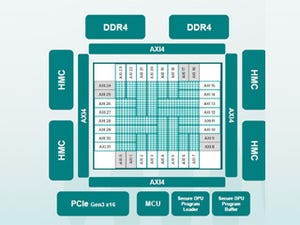

XilinxのVirtex UltraScale+ HBMファミリは、同社の第4世代の3次元LSIであり、FPGA自体が3チップで構成されており、これらのチップをシリコンインタポーザに搭載して接続して大きなチップとしている。XilinxのハイエンドFPGAでは、これまでもこのやり方が使われていたが、今回は、そのシリコンインタポーザに2個のHBM2メモリを搭載している点が新しい。

FPGAの製造は、TSMCの16FF+プロセスを採用し、 2.8M個のシステムロジックセル、9024個のDSPブロック、合計341Mbitのオンチップメモリを集積している。さらに、このFPGAは2666MHzのDDR4インタフェースを4チャネル、32.75GbpsのSerDesを96個、8チャネルの100G Ethernet、4チャネルの150G Interlaken、6チャネルのx8 PCI Expressポートを持っている。なお、この内の4チャネルのPCI ExpressはCCIXポートとして使うことができる。

そして、シリコンインタポーザには2個のHBM2メモリが搭載され、メモリインタフェースは、1024bitのデータとECC用の128bitの信号を1.8Gbpsで転送する。HBM2メモリの容量は、2個合計で8GBである。

|

|

VIRTEXと書かれたチップは3チップをつないだFPGAである。その下に2個のHBM2チップが見える。TSMCの16FF+プロセスで製造されている (このレポートのすべての図は、Gaurav Singh氏のHot Chips 29での発表資料のコピーである) |

次の図に、UltraScale+ HBMファミリの製品の一覧とその諸元を示す。ファミリにはFPGAチップが1、2、3チップのバリエーションがあり、さらに、1チップの製品にはHBM2が1個の製品がある。

次の図にVirtex UltraScale+ HBM(VU+HBM)の主要な特徴が書かれている。16nmプロセスで製造されるFPGAチップにはハードウェアのHBM2コントローラが搭載されており、HBM2コントローラは230GB/sのバンド幅を持つ。そして、ハードのAXIスイッチを持ち、2個のHBM2の間で統一されたメモリアクセスを可能としている。

FPGAチップにはハードIPのPCIeのコントローラが搭載され、このハードIPはCCIXプロトコルをサポートしている。

|

|

16nmプロセスで製造されるFPGAチップには、HBMコントローラ、CCIXプロトコルをサポートするPCIeポートが搭載されている。また、2個のHBM2メモリが搭載されており、FPGA本体とはシリコンインタポーザで接続されている |

DDR4 DRAMを使うVU7PF FPGAの場合は、メモリバンド幅は85GB/sで消費エネルギーは約27pJ/bitであったが、HBM2 DRAMを使うVU37P FPGAでは、バンド幅は460GB/s、消費エネルギーは約7pJ/bitである。つまり、バンド幅は5倍に増加し、消費電力は1/4に減少している。消費電力の減少は、FPGAとの間の配線が短く、信号線の寄生容量が減少したことと、信号振幅が小さくなったことが効いている。

ただし、HBM2は1対1接続しかできず、VU37Pの場合8GBの容量になってしまう。これに対してDDR4 DIMMを使えばもっと大きな容量のメモリを接続できるという違いがある。

HBM2あたり8チャネルのメモリコントローラ(HBM MC)が設けられており、コントローラは2つの64bit幅のスードチャネルを持っている。2つのスードチャネルはコマンドとアドレスバスをシェアしている。

各チャネルの信号は128bitであるが、それぞれのスードチャネルは256bit幅であるので、HBM2との1.8Gbpsの1/4の速度でAXIインタフェースに接続される。

次の図は、4つのマスタがHBM2の4つのチャネルを使うという使用状況でのHBMメモリのインタフェースの効率を測定したものである。5組の棒グラフがあるが、UNRと書かれた3番目の組は4つのマスタがどのチャネルにもランダムにアクセスするというもので、PTPと書かれているその他の4つの組は、マスタとHBMチャネルが1対1に対応するPoint-to-Point接続の場合である。

そして、最初の2つの組はメモリアクセスのアドレスがリニアに変わるアクセス、最後の2つの組はアドレスがランダムに変わるアクセスである。そして、PTPはマスタとチャネルの対応が一番近くなる対応で、PTPWは一番遠くなる対応となっている。

各組の3本の棒グラフは、左からReadWrite、ReadOnly、WriteOnlyアクセスとなっている。

マスタとチャネルの対応がランダムに変化するUNRのケースはインタフェースの効率が60%~70%に低下している。PTPの場合はReadOnlyの場合は90%を若干超える効率となっているが、ReadWriteが混在すると70%から80%の効率に低下している。