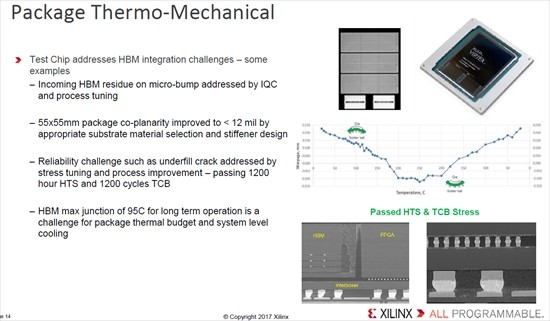

次の図の一番上の写真に示すように、3個の横長のFPGAチップと下にある2個のHBM2スタックがシリコンインタポーザに搭載されている。しかし、このパッケージングでは、いろいろな問題が発生し、解決が必要となったという。

重ねるチップ間を接続するマイクロバンプの表面に汚れが残る問題は受け入れ検査やプロセスのチューニングで解決した。

また、シリコンインタポーザは組み立て時の熱ストレスで反りが発生する。プラスの反りは上方に突、マイナスの反りは下方に突であり、この図で見ると、全体には上に突に反っているが、中央付近ではわずかに下に突になっている。この問題は、素材の材質とスティフナーで解決した。チップの下のアンダーフィルが割れる問題は、ストレス量の調整やプロセスの改良で乗り越えた。HBMのジャンクション温度を95℃に抑える必要がある点は、パッケージの熱特性の調整とシステムレベルの冷却で解決したという。

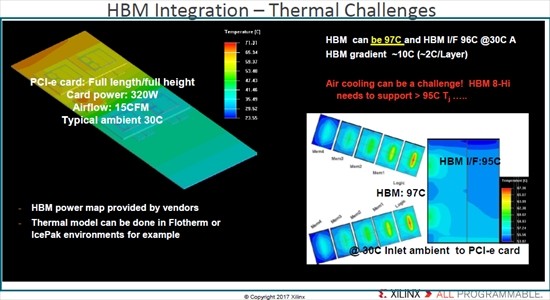

興味深いのは次の図で、左の図はフルサイズのPCIeカードの温度分布、右の図はHBM2スタックの各チップの温度分布を示す図である。どちらもFlothermやIcePakなどのCADで解析したものである。

解析の条件は、PCIeカードの消費電力は320W、冷却風量は15cfm(Cubic Feet per Minute、1cfm=472cm3/s))、取り入れ口の空気温度は30℃である。6個のVU-HBMが搭載されており、ボードの左側は65℃以上となっている。

右側のHBMの温度分布の図では、斜めに並んだ5枚の温度マップが、右側からロジックダイ、第1層DRAM、第2層DRAM~第4層DRAMのものとなっている。ロジックダイの中心は65℃以上の温度になっているが、DRAMの発熱は小さいので、第4層のDRAMでは中心部でも35℃程度の温度に留まっている。

この図では詳細な温度は分からないが、HBMの最大温度は97℃になり、HBMスタックの温度勾配は2℃/層という。4層のHBMでもぎりぎりの値で、8層のHBMの場合は接合温度は95℃を超えてしまうという(この部分の記述と温度分布の図とはかならずしも一致していない)。

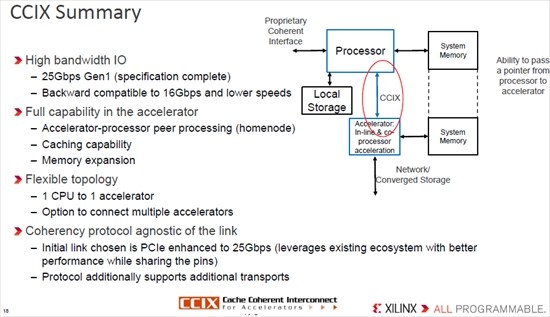

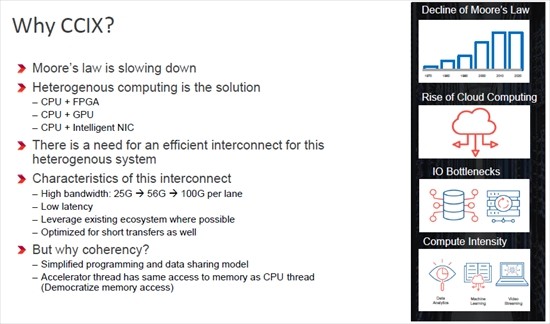

CCIXはCache Coherent Interface for Acceleratorsの略称で、CCIXコンソーシアムにはXilinxを始めとして、プロセサメーカーではAMD、ARM、IBM、Qualcommなどが参加している。また、メモリメーカーではSamsung Electronics、SK Hynix、Micron Technologyといった大手が参加している。

CCIXは、プロセサとアクセラレータやメモリなどを高バンド幅、かつ、短レーテンシでつなぐ新しい規格を作ろうという活動で、その接続はEthernetやInfiniBandのようにデータを送るだけではなく、コヒーレンシを維持する接続である点が特徴である。コヒーレンシを維持すれば、CPUとアクセラレータのメモリを一体として扱うことができ、アプリケーションの作成が容易になるのでサポートすると説明されている。

|

|

なぜCCIXかと言うと、ムーアの法則がスローダウンしており、それを乗り越えるにはヘテロな処理アーキテクチャが必要になる。そして、ヘテロなプロセサ間の接続には、高バンド幅、短レーテンシに加えてコヒーレンスが必要になるからである |

すでに仕様が完成しているCCIXの第1版では、レーンの通信速度は25Gbpsで、アクセラレータがCPUと同等にメモリアクセスし、メモリ拡張を行うことができる。コヒーレンシ維持のプロトコルはリンクに依存しないが、最初にサポートされるリンクは25Gbpsに拡張されたPCIeである。

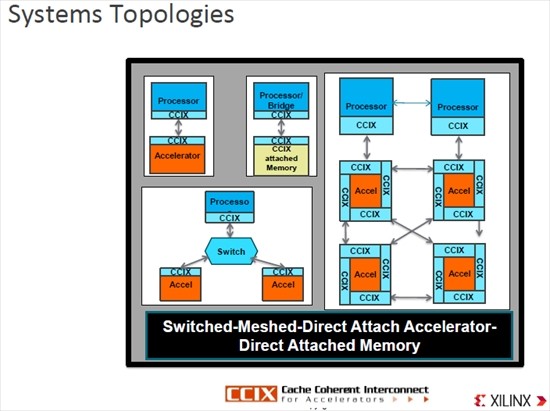

システムのトポロジは、CPUとアクセラレータをCCIXで1対1に接続したり、CCIX接続の拡張メモリを接続したりするのが基本的なものである。そして、CCIXスイッチを使って2台のアクセラレータを接続したり、右の図のように、2台のCPUに4台のアクセラレータのクラスタを接続したりするという形態がとれる。

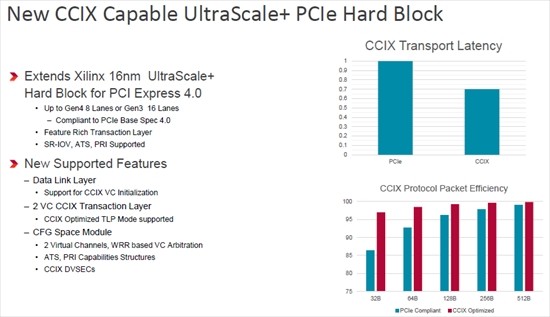

VU+HBM FPGAでは、PCIeのハードブロックがCCIXのプロトコルをサポートしている。CCIX接続には、PCIe Gen4のx8あるいはGen3のx16レーンを使用する。

右側の2つのグラフは、上側がCCIXのデータ伝送のレーテンシを比較するもので、PCIeでの伝送より30%高速になっている。右下のグラフは32バイト~512バイトのパケットを使った場合のパケット効率を比較するもので、PCIeでは86%程度の効率であるのに比べて、CCIXでは97%という高い効率が得られている。512バイトパケットでは、98.5%と100%であまり大きな違いはないが、CCIXプロトコルは短いパケットの場合でも高いパケット効率が得られることを示している。

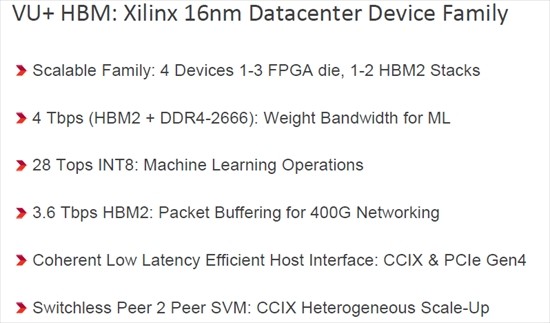

16nmプロセスを使うXilinxのデータセンター向けのVU+HBMファミリは1~3個のFPGAダイを使い、2個、または1個のHBM2スタックメモリを搭載する4種類のスケーラブルな製品である。

HBM2のバンド幅は3.6Tbpsで、DDR4を合わせたメモリバンド幅は4Tbpsに達する。そして、INT8で計算を行う場合は、マシンラーニング計算を28Topsで行うことができる。

また、コヒーレントで低レーテンシの効率の高いホストCPUインタフェースであるCCIXを装備している。

FPGAによる各種機能の実現は、特定の用途に限れば、実装密度や性能の点でカスタム設計されたLSIには及ばない。しかし、仕様に変更があっても合成するハードウェアを変更して対応することができるし、Microsoftがやっているように、データセンターの処理負荷に応じて実現する機能を変えるというダイナミックな運用をすれば、GPUやカスタム設計の専用LSIよりも処理コストを下げることもできそうである。このため、ハイエンドのFPGAは、データセンターでは不可欠なデバイスとなりつつある。