2011年6月20日~23日に掛けて、アメリカはTexas州のSan Antonio市郊外にあるJ.W.Marriott San Antonio(Photo01,02)において、「Freescale Technology Forum(FTF) Americas 2011」が開催された。昨年まではFlorida州Orlandoでの開催だったが、今回は同社のお膝元(Freescaleの本社はTexas州Austinにあり、San Antonioから車で1時間ほどの距離である)に移しての開催である。

ちなみにこの建物の正式名称は"JW Marriott San Antonio Hill Country Resort & Spa"で、名前の通り完全なリゾートホテルである。San Antonioを東西に貫く高速281号線からTPC Gatewayという脇道に入った先に位置するが、このTPC Gatewayに入ってなだらかな丘を抜けると、そこは超高級住宅街である。そこからさらにもう1つ丘を越えた先にあり、結果として水平線を見渡しても他の建物がほとんど目に入らないという、日本ではちょっと考えられない類のリゾートである(そういえば、Orlandoでの会場だったJW Marriott Orlando Grande Lakesも、隣接する湖がまること自分のところの所有物という、これもこれで壮絶なリゾートであったが)。

まぁ建物の説明はこの位にしておくとして、FTFはFreescaleの新製品発表の重要な場でもあり、今回も盛りだくさんの発表が行われた。ということでまずは(すでに記事もあがっているが)QorIQ AMPシリーズの話をご紹介したいと思う。このQorIQ AMP、同社CEOであるRich Beyer氏の基調講演の最初のテーマとして登場したほどで(Photo03~05)ある。

|

|

|

|

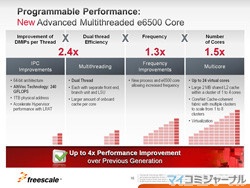

Photo03:「何と比べてか?」という話はここには出てこないが、これは現行のQorIQ P4080と比べて。数字を全部掛け合わせると、約4.3倍の高速化ということになる |

Photo04:消費電力は最大50%減。これもおそらくP4080と比較しての数字であろう。どうやって、という話は後で触れる |

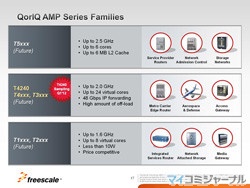

Photo05:QorIQの3シリーズ。2011年2月のMWC(Mobile World Congress)でe500コアにStarCore DSPを組み合わせたQorIQ Convergeを発表しており、今回のQorIQ AMPが第3世代という扱いになる |

これに関しては、さらに同社のLisa Su氏(Photo06)のセッションの中で細かい話が紹介されたのでまずこちらのスライドから紹介したい。基本的にQorIQ AMPは現在のQorIQの後継という扱いになる。なのでQorIQ Convergeなどとは異なり、基本的にはWire Network向けの製品ということになる(Photo07)。

|

|

|

Photo06:Senior Vice President and General Manager, Networking and MultimediaのLisa T. Su博士。もうすっかり同社の顔の1人でもある |

Photo07:このため、QorIQ AMPは(もちろんいくつかのアクセラレータは入っているが)基本的には超高速汎用プロセッサ的な構成となっている |

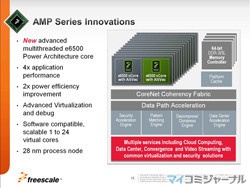

その内部構成であるが、大きな特徴は28nmプロセスによる製造と、Multi-Threadingの搭載という事になる(Photo08)。

|

|

Photo08:最大24のVirtual Coreというあたりがちょっとポイント。ちなみに図のプロセッサは、2つのVirtual Coreを1つにまとめて表示していて、物理的なCPUのクラスタの話ではない(これは後述) |

実はこのプレゼンテーションを見て「さすがに4倍はないよな」とちょっと笑ったところ、Su氏に見つかって「笑い事じゃないのよ。本当に顧客には300%とか400%の性能向上を求められているのだから!」と怒られてしまったのだが、ではその400%をどうやって実現したのか、がこちらである(Photo09)。

Photo03ではIPCの改善を1.4倍、SMTによる性能改善を1.7倍としており、さらに周波数の引き上げ(1.5GHz→2GHz)、コア数の増加(8Core→12Core)でトータル4倍超、という計算になるとしている。

ちなみに製品ラインナップだが、QorIQのPシリーズ同様に、T1~T5までの5つのラインナップになることが明らかにされており、今回説明された物理12コア/仮想24コアの製品は、T4のハイエンドであるT4240となることが明らかにされた(Photo10)。性能に関しては先の記事でいくつか数字が挙がっているが、トータルとして40GbpsクラスのL4~L7スイッチが構成できるレベル、という位置づけである。