東北大学(東北大) 省エネルギー・スピントロニクス集積化システムセンター(CSIC) センター長の大野英夫教授のグループは、NECなどと共同で電子の電荷とスピンを利用したスピントロニクス技術に基づく待機電力ゼロの低電力スピントロニクス・システムLSIの実証、および高信頼性垂直磁化スピントロニクス不揮発素子の開発に成功したことを発表した。

同研究は、日本学術振興会の最先端研究開発支援プログラム「省エネルギー・スピントロニクス論理集積回路の研究開発」において実施され、同研究の詳細は、2011年6月13~17日に京都で開催される半導体回路技術に関する国際会議「VLSI回路シンポジウム(2011 Symposium on VLSI Circuits)」にて発表される。

スピントロニクス素子による不揮発プロセッサ

半導体デバイスは、集積度の向上による高機能化に伴い電力消費の限界に達した際に新しいデバイス構造に置き換わり発展してきた。過去にはバイポーラ集積回路からCMOS集積回路へ、現在はCMOS集積回路からマルチコアLSIへ移行している。

トランジスタの微細化に伴い、高機能化したシステムLSIではトランジスタの漏れ電流による待機電力が動作電力に迫っており、待機電力の抑制が課題となっている。そこで東北大学 大野教授のグループは、次世代の半導体デバイスとして「不揮発プロセッサ」の開発を進めている。従来のプロセッサは電源をOFFにする際にプロセッサの内部情報を外部記憶に保存していたが、電源OFFでも記憶を保持できる不揮発素子を組み込み、待機電力ゼロのシステムLSIを実現する。なお、不揮発素子にはシステムLSIに必要な基本性能を備えるスピントロニクス素子を導入する。

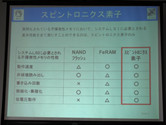

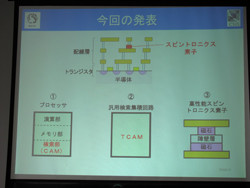

今回のVLSI回路シンポジウムで発表する内容は、スピントロニクス素子で不揮発プロセッサを実現するため開発と要素技術に関するもの。具体的には、スピントロニクス素子を用いた、(1)連想メモリプロセッサ、(2)汎用検索集積回路、(3)高性能スピントロニクス素子の3件を発表する。

連想メモリプロセッサの開発

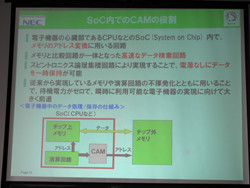

まずNECとの共同研究では、CPU内で用いられる連想メモリプロセッサ(CAM)において、既存回路と同等の高速動作と、電源OFFでもデータを保持できる不揮発動作を両立する回路を開発・実証した。電子スピンと電荷の両方を利用するスピントロニクス論理集積回路技術に加え、NECが従来から開発を進めている垂直磁壁素子をCAMに適用したもの。CAMはCPUなどのSoC内でメモリのアドレス変換に用いる回路であり、CAMを不揮発性とすることで電源なしでのデータ保存が可能となり、待機電力ゼロのプロセッサを実現できる。

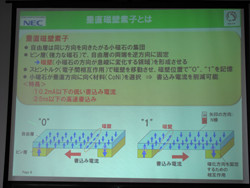

垂直磁壁素子は、同じ方向を向きたがる小磁石の集団である「自由層」と強力な磁石である「ピン層」からなり、自由層の両端にピン層を逆方向に固定させることにより、自由層の小磁石の方向が急峻に変化する「磁壁」を形成している。この磁壁をスピントルクにより移動させることで、磁壁に位置により"0"、"1"を記憶する。MRAMなどにおける磁場による書き込みは電流が大きいが、垂直磁壁素子は0.2mA以下の低い書き込み電流を実現している。また、書き込み速度は5ns以下となっている。

今回の開発では、垂直磁壁素子を3端子構造とした。書き込み電流と読み出し電流の経路を別にしたことで、電流の向きだけで書き込み制御が可能となり、簡便な書き込み制御により高速化を実現した。また、書き込み電流経路に抵抗がなく直列接続が可能となり、さらに書き込み用スイッチを共通化した。これにより、トランジスタ数は2セル当たりのトランジスタ数を従来のCMOSの8個から3個となり、CAM面積を約1/2に削減した。

90nm CMOSプロセスと140nm幅の垂直磁壁素子プロセスを採用し、16kbのCAMを330×460μmのサイズで実現している。

汎用検索集積回路の開発

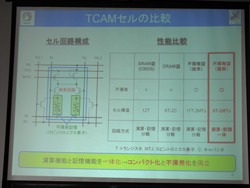

さらにNECとの共同開発で、待機電力フリーの汎用検索集積回路(TCAM)を開発した。TCAMはネットワークルータのウィルスチェッカーやデータベースマシンのデータ検索ハードウェアとして用いられており、情報検索を高速・高並列に実行する。一方で、待機時間の長さから、待機電力の抑制が課題となっている。

今回の開発では、スピントロニクス技術を用いることで不揮発記憶機能と演算機能をコンパクトに一体化させ、データセンターにおいて待機電力ゼロによる低電力化と小型化による大容量化を実現する。具体的には、スピントロニクス技術であるスピン注入磁化反転型磁気トンネル接合(MTJ)デバイスとシリコンデバイスを組み合わせた不揮発ロジックインメモリ回路技術を導入し、従来のTCAMセル回路の半分程度のトランジスタ数で不揮発化を実現した。

また、セル回路内部にダイオード接続トランジスタを挿入し、セル回路における一致・不一致の結果に応じてダイオード接続トランジスタの動作ポイントを変更することで、実用途で用いられる数百ビット以上の多ビット並列検索動作を実現した。これらの開発について、試作チップにより基本動作を実証した。

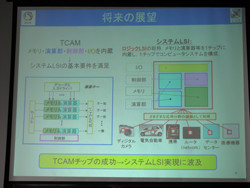

なお、TCAMはメモリ、演算部、制御部、I/OといったシステムLSIの基本コンポーネントで構成されており、TCAMチップで不揮発化を実現することで、システムLSIに不揮発化の実現の可能性が高まるという。

高性能スピントロニクス素子の開発

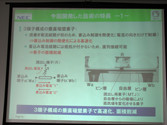

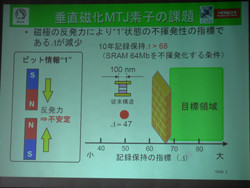

要素技術としては、日立製作所との共同開発で、不揮発性を高めた新構造MTJ素子を開発した。MTJ素子では、記録層と参照層の2つの磁性層の磁化方向が同じであるビット情報"0"に対し、磁化方向が対抗するビット情報"1"の状態は磁化の反発力が発生し、不揮発性の状態が不安定となることが課題となっている。10年以上の記録保持を実現するためには、不揮発性の指標である熱安定性Δが68以上必要であるが、直径100nmの垂直MTJ素子ではビット情報"1"状態のΔは47となっている。

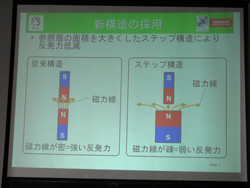

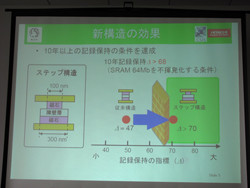

今回の開発では、MTJ素子の構造として新たにステップ構造を導入した。従来のMTJ素子は記録層および参照層の直径が同じ構造だったが、ステップ構造では記録層より下の参照層の直径を大きくした。これにより、磁性層間の磁力線を疎にすることで反発力を低減する。記録層直径100nmおよび参照層直径300nmとしたステップ構造では、ビット情報"1"状態のΔは70以上に向上し、10年以上の記録保持の条件を満たした。また、今回実証したステップ構造のMTJ素子のセル面積は32nmノードのSRAMとほぼ同じであり、さらに参照層を200nmまで縮小可能で20nmノードへ応用できる。

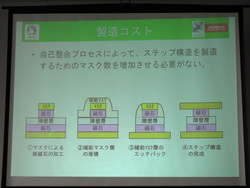

なお、ステップ構造は自己整合プロセスによりマスク数を増加させずに製造が可能となっている。

実用化に向けた開発を推進

今後の展開としては、開発支援プログラムが2013年まで継続するため、プログラム終了までにSoCの不揮発化を実現する方針。その後3~4年をめどにさまざまな電子機器に対して不揮発プロセッサの導入を進める。

まだ具体的なアプリケーションは想定できないため、現時点ではデバイスのスペックも定まっていないという。デバイスの配線層に配置するスピントロニクス素子の位置によって、デバイスの性能が変わってくるが、今後のニーズを見て対応することになる。

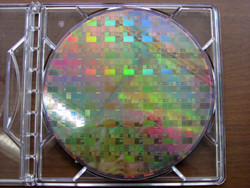

今後の課題としては、設計から製造プロセスまでを完成させる必要がある。デバイスを使いこなすためのアーキテクチャやソフトウェアなどを順次開発していく方針。また、信頼性も製品レベルにはまだ到達していないため、つくばイノベーションアリーナ(TIA)のクリーンルームで300mmウェハによる検証を進めて行く。製造プロセスについては、磁性体素子のエッチング技術を新たに開発する必要があり、製造装置メーカーとの連携を進めているという。