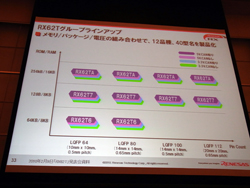

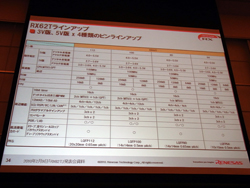

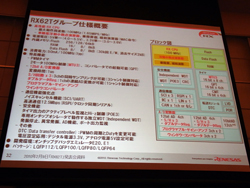

ルネサス テクノロジは2月9日、同社の次世代マイコン「RX」ファミリの第3弾製品として民生機器などのモータ制御機器向け32ビットマイコン「RX62Tグループ」12品種、40型名を製品化したことを発表した。2010年3月から順次サンプル出荷を開始、同年12月より月産10万個で量産を開始、2012年には月産100万個規模まで引き上げる計画。

|

|

ルネサス テクノロジ 取締役 マイコン統括本部 本部長の水垣重生氏 |

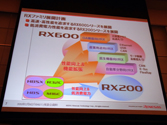

RXシリーズは、既存の32ビットCPUコア「H8SX」および「R32C」、16ビットCPUコア「H8S」および「M16C」を継承し、「20年先を見据えた性能、低消費電力を実現した次世代マイコン」(同社 取締役 マイコン統括本部 本部長の水垣重生氏)というもので、同製品は、同シリーズとして高速・高性能を追求した「RX600」シリーズに位置づけされるもの。

同社マイコンとしては、16ビットと32ビットをカバーするミッドレンジマイコンとしての立場だが、32ビットまでカバーできることについて水垣氏は、「2009年移行、システムの高機能化、高性能化が進み、それに伴うシステム制御の複雑化やプログラムの増大が課題となるほか、世界的なグリーンへの要求および開発期間短縮などが求められている。ルネサスとしてもこれまで16ビットが主流であったが、より複雑なシステムを扱いやすくすることを目指し、今後のメインターゲットを32ビットへとシフトしており、既存資産の使いまわしが可能なRXに期待している」と述べる。

今回発表されたRX62Tグループは、白物家電やインバータ制御を応用する民生機器向けという位置づけで、これによりRXシリーズは2010年3月までにシリーズ累計合計79製品が展開されることとなり、さらに広い範囲で対応可能な3グループの開発が進められており、「2010年12月には次期RX600シリーズとしてさらに3グループ83製品を追加予定」(同)であり、シリーズ累計で162製品まで拡充する計画となっている。

|

|

ルネサス テクノロジ 汎用MCU製品技術部 部長の堀内健二氏 |

そのような背景の中で製品化されたRX62Tは、インバータのより細かな制御や太陽光発電などの新たなアプリケーションへの対応を図るために開発された製品群。そのため、「インバータ市場向けにフィードバック制御機能を強化した」(同社 汎用MCU製品技術部 部長の堀内健二氏)という。

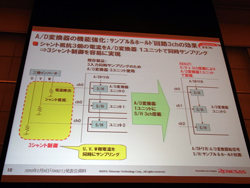

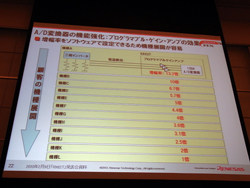

具体的には、まずはA/Dコンバータ(ADC)の機能強化が行われた。同マイコンに搭載されているADCは12ビットのものを2ユニット、10ビットのものを1ユニット搭載している。また、三相モータでは各相(U/V/W相)に流れる電流を同時にサンプリングすることが求められるが、同製品では12ビットADCの入力端子のうち3本それぞれに専用のサンプルアンドホールド回路(S/H)を搭載。これにより、タイマからのトリガでサンプリングを開始させることが可能で3シャント制御を1ユニットで実現することが可能となった。

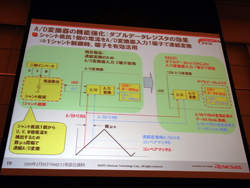

また、1シャント方式では、モータのキャリア周期ごとに任意のタイミングで2回のA/D変換が必要で、かつ1回目と2回目のA/D変換間隔が毎回変化することとなる。従来のマイコンでは、これに対応するために入力に2端子が必要であったが、同製品ではダブルデータレジスタ構造を採用。これにより、1入力端子で2つのデータの入力が可能となり、1回目、2回目のA/D変換結果がそれぞれのレジスタに格納され、A/D変換が終了した時点で、CPUがA/D変換値を同時に読むことで負荷軽減ができるようになった。

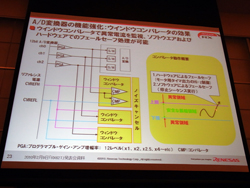

さらに、12ビットADCに1倍から13.3倍までソフトウェアで増幅率を設定することが可能なプログラマブル・ゲイン・アンプおよびハードウェアとソフトウェアによる監視が可能なウインドウコンパレータをそれぞれ3個内蔵。これによりモータのベクトル制御に使用する電流増幅用の外付けオペアンプや過電流・過電圧保護用のコンパレータを削減することが可能となった。

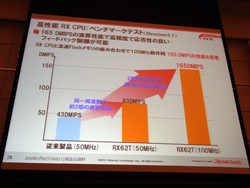

このほか、CPUのほか、演算の高速化を実現するためにFPUを搭載。これによりフィードバック制御時などの演算速度と演算精度の向上が可能となったほか、90nmプロセスを仕様することで、併せて0.5mA/MHzの低消費電力性も実現した。

加えて、最大2個の三相モータ駆動を実現するために新たに開発したマルチファンクション・タイマ・ユニット3(MTU3)と三相モータを1個駆動可能なこちらも新規開発の16ビット汎用PWMタイマ(GPT)を搭載したことで、最大3個の三相モータの同時制御を1チップで実現可能なほか、相補PWMモードにダブルバッファ機能を追加。これにより、従来のMTU2S比で割り込み回数を半減しつつ、割り込み間隔を2倍に広げることに成功した。

なお、同グループの最大動作周波数は100MHzで、100MHzでの1サイクルアクセスが可能なプログラム格納用の内蔵フラッシュメモリと組み合わせることで処理性能165DMIPSを実現している。