日本のベンチャーが5nmプロセスでAIチップを開発

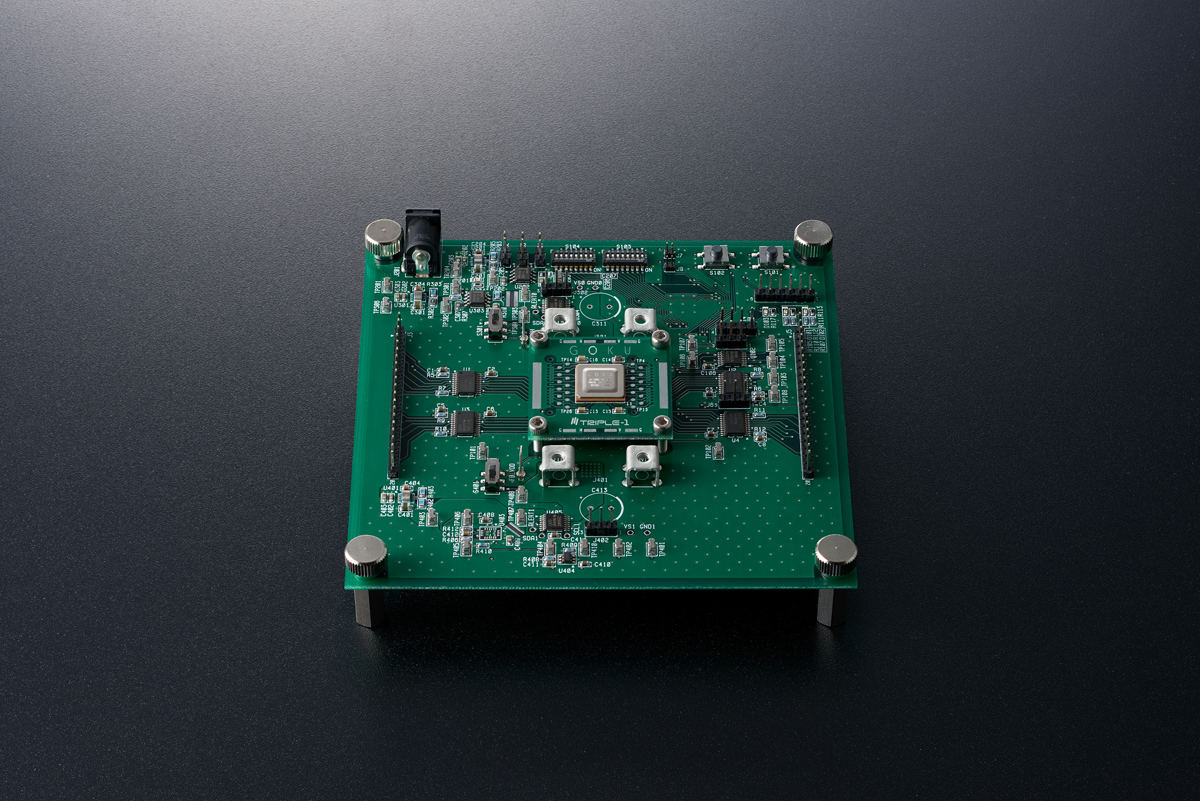

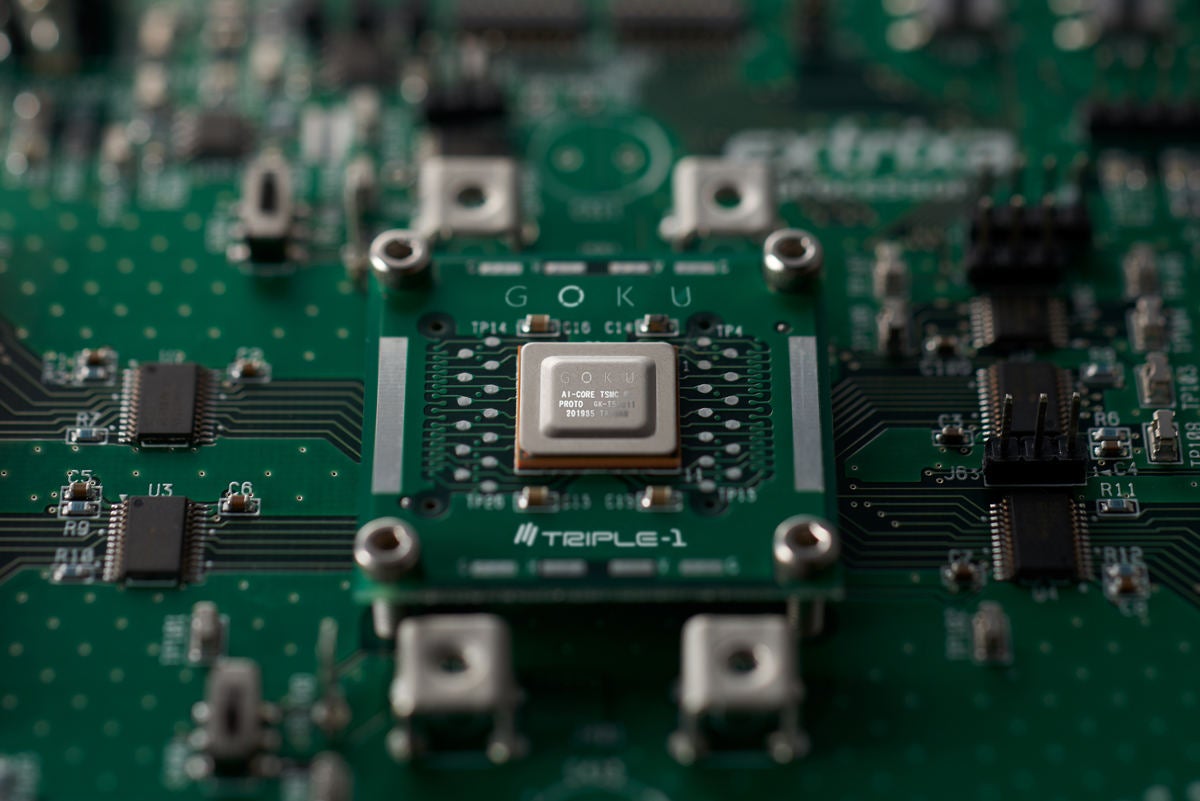

日本の半導体ファブレスベンチャーTRIPLE-1は、2020年初頭時点で世界最先端の半導体プロセスとなるTSMCの5nmプロセスを採用したディープラーニング向けAIプロセッサ「GOKU」の量産に向けた第1段階の試作品を2019年9月に完成させ、現在、性能評価などを進めていることを明らかにした。

同社は2016年11月に設立されたファブレスベンチャーで、2018年にもTSMCの7nmプロセスを採用したビットコイン用マイニングASIC「KAMIKAZE」を開発するなど、先端プロセスを活用した半導体設計を行ってきた。ちなみに、こちらについても開発が続けられており、現在、第2弾製品として同じ7nmプロセスを採用した「KAMIKAZE II」のRTL設計が完了した段階にあるという。

GOKUの最大のポイントは最先端プロセスおよび回路アーキテクチャの工夫による低消費電力化。同社の担当者は、消費電力はほかのディープラーニング専用チップと比べ、1/10程度まで下げることを目標としているという。このパフォーマンスと低消費電力の実現のカギを握るのが、10名ほどいる設計エンジニアたち。いずれも元々、日本を中心とした半導体ベンダで設計に長年携わってきた人たちで、そうして培われてきた技術が生かされているという。

また、回路設計の考え方もユニークだ。通常はパフォーマンスを引き上げるためにはトランジスタの駆動電圧を引き上げ、動作周波数を高める方法がとられるが、同社の考え方は真逆で、電圧を下げて、周波数も引き下げる。そうすると、確かに1つの乗算器あたりの演算性能は落ちるものの、必要とする電力は電圧の2乗に比例するので、低消費電力化に寄与することとなる。同社によれば、トランジスタの動作電圧としてTSMCが規定しているのが7nmで0.75V、5nmだと0.35Vで、これで500MHz駆動が可能だという。

ただし、「単純に電力を下げただけではまともに動かない。マイニングチップを7nmで実現していく中で、低電力で素子を駆動させるためのノウハウが培われてきた。そうした知見を活かすことで、高性能かつ低消費電力という方向性が見えた結果」であると、決して単純に数値を下げたらできるわけではなく、それだけの技術ノウハウを積み重ねてきたことを強調する。

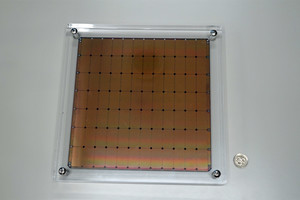

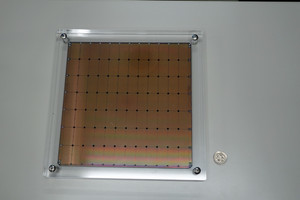

またディープラーニングの処理の場合、メモリとの関係性も重要になってくる。GOKUでもチップ内にSRAM領域を有しているが、そのサイズはロジック規模とのトレードオフの関係になる。量産品のダイサイズはフォトリソ工程において1ショットでとれるほぼ最大まで利用するとのことだが、ロジックの数を優先すると、どうしても不足しがちになる。そのため外部DRAMの活用も検討しているという。その候補としては、性能的にはHBMだが、コストが高かったり、必要とするインタフェースの回路面積が大きいなどの課題があるため、実際にはレイテンシが増えるといった問題をそれ以外のメリットで内包できるGDDR6かLPDDR5あたりが有力とみているとする。

さまざまなニューラルネットワークに対応

ディープラーニングのニューラルネットの進化は日進月歩で進んでいる。そのため、決まった処理を行うのであれば回路を固定した方が有利となる。しかし、それだとユーザーが違うニューラルネットワークを使いたい、と思ったときに使えなくなるというリスクを抱えることとなる。FPGAは、そこを逆手にとり、自由に試せる回路として評価が高まりつつあるが、GOKUも回路内の乗算器を使いたいニューラルネットごとに組み合わせを変更する機能を備えるという。ユーザーにはミドルウェアレベルの環境が提供され、その上で使いたいニューラルネットワークを構築する、という形になるという。

低消費電力でハイパフォーマンスなAIアクセラレータとなると、エッジ向けの製品(推論)を目指すかというと、どちらかというとデータセンターなどの学習を目指すという。ニューラルネットを変更できる、というのもそちらの方向性を意識したための仕組みだとする。

利用のアプリケーションとしては、クラウド越しにデータセンターのサーバにアクセス。そこでニューラルネットワークを自由に構築して、必要な学習を行う、といったものが想定される。そのために同社はモジュール化やサーバ構築などが得意な会社と協業できるのであれば、フレキシブルに対応を図っていきたいとしている。

初期量産のターゲットは2021年

今回のGOKUはあくまでディープラーニングコアを1個搭載した第1段階の試作品だと同社では説明している。この実チップを使って、1個のディープラーニングコアの内部にはどの程度の乗算器を搭載するのがベストであるのかといったことや、実際の処理の際の電力消費量はどの程度であるのかといった基本性能の評価が進められるほか、電圧のさらなる低減のためにはどのようなトランジスタセルを用いるべきか、どういった構成の回路が有用であるのか、といったことも調べていくとする。

すでに複数のディープラーニングコアを搭載する第2段階のテストチップの実現に向けた検討も進めているとしており、2021年の早い段階で製造にこぎつけ、それを踏まえて、2021年内に初期量産(おそらく限りなくエンジニアリングサンプルに近いものになるとみられる)にまでたどり着きたいとしている。

なぜ先端プロセスを選んだのか?

同社は従業員が30名も居ないほどのまさしくベンチャーである。そうした企業がなぜ先端のプロセスを使った半導体設計に挑んだのか。

同社は、「7nmの時もそうだったが、世の中になかったものに挑戦するというスタンスで進めてきた。実績に裏打ちされた設計エンジニアたちからも先端プロセスに挑みたいという声が多かった。5nmプロセスも、同じ理由でリスク生産としての提供のタイミングながらも、7nmでの成功体験もあったため、果敢に挑戦するという話になり、それほどリスクは感じなかった」と、先端プロセスを選択し続ける理由を説明する。また、ディープラーニングコアの専用チップ分野は先端プロセスを採用する製品がそれほど多くなく、実際の量産までに多少時間がかかっても、アドバンテージを得やすい、という読みもあるという。

なお、今回の試作品では通常のEUVによる5nm、いわゆるN5プロセスを使って製造されたが、TSMCでは2021年の上半期より改良版プロセスであるN5+の量産を開始する予定としている。そのためTRIPLE-1でも量産にはN5+を採用していく計画とするほか、次世代品についてもタイミング次第で、現状では読めないとしつつも、メジャーアップデートのプロセスに位置づけられている3nmの活用なども検討していきたいとしている。