TSMCは、同社のエコシステムパートナーであるOpen Innovation Platform(OIP)メンバーカンパニーに対し5nmプロセスを用いた設計基盤の提供を開始したと発表した。同社は、このような5nm設計基盤の提供は世界の半導体業界に先駆けるものであるとしている。

同社の5nmプロセス向けの設計基盤として用意されるのは、5nmデザイン・ルール・マニュアル(DRM)、SPICEモデル、プロセス・デザイン・キット(PDK)、シリコン検証済みのファンデーションおよびインタフェースIP、認定電子設計自動化(EDA)ツールによる設計フローサポートなどである。

TSMCは、設計エコシステムパートナーである 米Cadence Design Systems、米Synopsys、Mentor Graphics(Siemens)、およびANSYSなどと協業してTSMC OIP EDAツール認証プログラムに沿ってEDAツールの認証作業を完了した。そして、EDAおよびIPベンダは、TSMCと共同で、これらの設計基盤を多数のシリコンテストビークルを用いて開発し検証を行ったという。

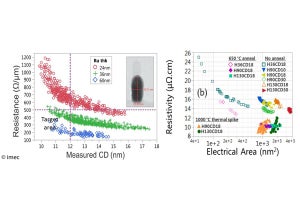

TSMCの5nmプロセスは1世代前の7nmプロセスと比較して、Arm Cortex-A72コアで1.8倍のロジック密度と15%の速度向上を実現できるとともにSRAMなどの専有面積も最少化できるとしている。TSMCは、7nmプロセス第2世代(N7+)でごく一部の工程でEUVリソグラフィを採用し始めたが、5nmプロセス(N5)ではEUVリソグラフィを本格的に採用することにより、従来の多重露光を用いた複雑なプロセスを簡略化でき、歩留まり向上効果が得られると説明している。

TSMCによると、5nmプロセスは、次世代の高度なモバイルおよび高性能コンピューティング(HPC)向け低消費電力SoC設計を可能にし、成長が期待される5Gおよび人工知能(AI)市場をターゲットにしているという。

なお、TSMCの研究開発/技術開発担当バイスプレジデントであるCliff Hou氏は、「TSMCの5nm技術は、AIと5G分野の需要増大に対応するための業界最先端のロジックプロセスを顧客に提供するもの。5nm技術では、今まで以上に設計とプロセス技術の同時最適化が必要であり、そのため、私たちはエコシステムのパートナーとシームレスに協力して、シリコン検証済みのIPブロックとEDAツールを顧客がすぐに使えるように取り組んできた」と述べている。同氏は「顧客はすでにデバイスの設計に向けた取り組みを開始しており、製品のテープアウト、パイロット生産および早期サンプリングの道が開けた」としており、2019年前半に顧客からの受託製品テープアウト、後半に試作、2020年前半に量産開始を予定している。