前回は、半導体製造の8工程のうち7つ目となる、良品判定を行う「テスト工程」についてご紹介しました。今回は半導体製造の最後の工程となる「パッケージング工程」をお届けします。

7つ目の工程であるテスト工程の終了後、完全な半導体に仕上げる最後の手順がパッケージング工程です。スマートフォン本体の中の回路基板に小さな黒い長方形のものがあるのを見たことはありますか? 表面のチップ構造は、内部の壊れやすい集積回路を保護するだけでなく、放熱やチップの分離に役立つほか、最も重要な点として、回路基板と他の素子を接続する役割を果たしています。半導体を外部から保護して電気的に接続する製造手順は「パッケージング」と呼ばれています。パッケージング工程を経て、おなじみの半導体チップが完成します。では、最後の工程、パッケージングを詳しく見てみましょう。

半導体を保護して接続する「パッケージング工程」

これまでの工程で作られたウェハには、同じサイズでさいの目状のチップである「ダイ」があります。このチップを切り分ける工程を経て、各チップが使えるようになります。切り分けたチップは、外部環境によって損傷する可能性があり、電気信号をやりとりできなくなる恐れがあるため、分離処理を行う必要があります。

この処理には、半導体チップを安全に保護するために封入し、外部と電気信号をやりとりできるように接続するパッケージング工程が含まれます。パッケージング工程は、ウェハの切断、ダイの接着、相互接続、成形、パッケージング・テストで構成されます。各手順について説明します。

パッケージング工程1:ウェハの切断/ダイシング

ウェハ上に密集している無数の完成チップを切り分ける前に、ウェハの裏側を研磨してパッケージングに十分な厚さにする「バック・グラインド」工程を行います。この手順の後に、チップを切り分けるためのウェハ上のスクライブ・ラインに沿って半導体チップを切断します。

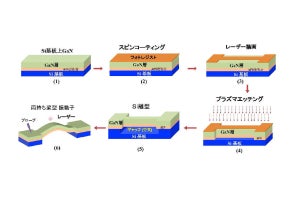

ウェハの切断には、「ブレード・ダイシング」、「レーザー・ダイシング」、「プラズマ・ダイシング」の3つの方法があります。ダイヤモンド微粒子でコーティングされた薄いブレードを使用するブレード・ダイシングは、広く用いられている手法です。レーザーを使用するレーザー・ダイシングは、薄いウェハや狭いスクラブ・ラインでも容易に切断できます。プラズマ・エッチングを用いるプラズマ・ダイシングは、極めて狭いスクラブ・ラインでも有用性に優れています。

パッケージング工程2:ダイの接着

ウェハのチップをすべて切り分けたら、各チップ(ダイ)を基板に接着します。ここで、基板として使用するリード・フレームが、電気信号をやりとりできるように半導体チップを外部の回路に接続し、保護する役割を果たします。チップは、液状接着剤またはテープ型の固形接着剤を使用して基板に固定できます。

パッケージング工程3:相互接続

チップを基板に固定したら、電気信号をやりとりできるようにチップと基板の接点を接続します。この接続は、方法によって、金属細線を使用するワイヤ・ボンディングと、ボール状の金またはスズのバンプを使用するフリップ・チップ・ボンディングに分類されます。ワイヤ・ボンディングは従来の方法で、フリップ・チップ・ボンディングは半導体の速度を向上させるために用いられます。

パッケージング工程4:成形

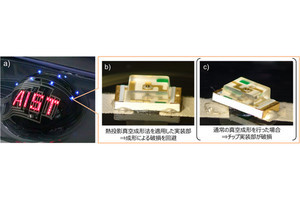

半導体チップを接続したら、半導体集積回路を温度や湿度などの外部環境から保護し、パッケージの形状にする成形工程を行います。意図するパッケージの形状に成形し、半導体チップとエポキシ樹脂成形材料(EMC)を型に入れて封止します。これで、半導体の形状に仕上がります。

パッケージング工程5:パッケージング・テスト

前述の工程で成形した最終的な形状で、最後に不良品テストを実施します。この最終テストでは、最終製品としての形状で半導体を調べます。この工程では、半導体を検査装置に入れ、電圧、温度、湿度などのさまざまな条件を設定し、電気特性および機能特性と速度をテストします。テスト結果は、不良品を判断するためだけでなく、品質や生産効率を向上させるためのデータとしても活用されます。

パッケージング技術の進化

より小さくて強力なチップを実現させるための多くの技術的な変化に伴い、パッケージングはここ数年で進化しています。ラムリサーチは、ウェハレベル・パッケージ(WLP)、バンピング、再配線層(RDL)などのバックエンド工程に成膜を適応する次世代のパッケージング技術戦略とエッチングや洗浄などのフロントエンドのウェハ製造技術に取り組んでいます。

続いて、ラムリサーチのソリューションによって可能になる高度なパッケージングを紹介します。

高度なパッケージングとは?

従来のパッケージングでは、ウェハを切り分け(ダイシング)、チップをパッケージに入れます。高度なパッケージングの1つとしてウェハレベル・パッケージ(WLP)があり、ダイがウェハ上にある状態でパッケージングします。

WLP工程では、ウェハのパッケージングとテストを行ってからチップを一斉に切り分けて最終製品にするため、従来のパッケージング工程よりも生産コストを削減できるというメリットがあります。

高度なパッケージングは、1種類のダイを小型のパッケージに入れる「2Dパッケージング」、信号を平面にルーティングして2種類以上のダイを一緒にパッケージングする「2.5Dパッケージング」、信号を垂直にルーティングして2種類以上のダイを一緒にパッケージングする「3Dパッケージング」に分類されます。

小型2Dパッケージング

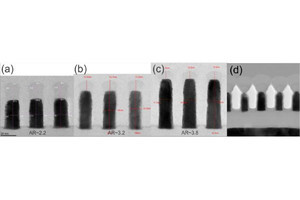

上記で説明したとおり、パッケージング工程の主な目的の1つは、半導体チップの信号を外部に送信することです。ウェハ形状の上にバンプを形成し、入力/出力信号を送信します。このバンプ形成には、チップの面積内で形成する「ファンイン」と、チップよりも大きな面積で形成する「ファンアウト」があります。ここで、入力/出力信号を「I/O」と呼び、入力/出力数を「I/Oカウント」と呼びます。

I/Oカウントは、パッケージング方法を決定する重要な要素です。I/Oカウントが小さい場合は、ファンインのパッケージング工程を行います。パッケージとチップのサイズが同等であるため、この工程はチップ・スケール・パッケージ(CSP)またはウェハレベル・チップ・スケール・パッケージ(WLCSP)と呼ばれています。I/Oカウントが大きい場合は、たいていファンアウトのパッケージング工程を行い、信号を送信するためにバンプの他に再配線層(RDL)が必要になります。この工程は、ファンアウト・ウェハレベル・パッケージ(FOWLP)とも呼ばれています。

2.5Dパッケージング

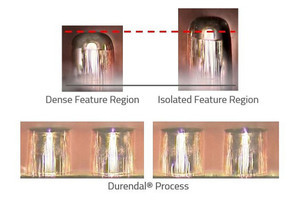

2.5Dパッケージングは、信号を平面にルーティングし、2種類以上のチップを1つのパッケージにまとめる手法で、パッケージのサイズと性能が向上します。最も広く用いられている手法では、シリコン・インターポーザを使用し、メモリとロジック・チップを1つのパッケージにまとめます。2.5Dパッケージングには、シリコン貫通電極(TSV)、マイクロバンプ、微細ピッチRDLを形成するコア技術が必要です。

3Dパッケージング

3Dパッケージングは、信号を垂直にルーティングし、2種類以上のチップを1つのパッケージにまとめる手法で、半導体チップの小型化が可能になり、大きいI/Oカウントに対応できます。I/Oカウントが大きい場合にはTSVが使用される一方で、I/Oカウントが小さい場合にはワイヤ・ボンディングが使用され、垂直に配置されたチップに信号システムを構成します。3Dパッケージングには、TSVとマイクロバンプを形成するコア技術が必要です。

ラムリサーチは、シリコンエッチング、金属拡散バリア、銅めっき、クリーニングといった必須のコア・ソリューションだけでなく、マイクロバンプと微細RDLを形成するために必要な電気めっきやクリーニング、ウェットエッチングなどのさまざまなソリューションを提供しています。

こうして8つの製造工程を経て、半導体チップは製品として完成し、私たちの身の回りにあるさまざまな製品に搭載されます。今回で「半導体製造の8つの工程」シリーズは終了となりますが、半導体製造について理解を深めいていただけましたら幸いです。最後までお読みいただきありがとうございました。

パッケージング工程関連用語

バック・グラインド

ウェハの裏側を研磨してパッケージングできるように薄くする工程。

スクライブ・ライン

チップ(ダイ)を切り分けるためのウェハ上の線。