zEC12メインフレームのプロセサについては、昨年のHot Chips 24で発表されている。しかし、zEC12の製品発表の翌日がHot Chips 24での発表日であり、発表スライドの準備時点では正式名称が確定していなかったので、zNextという名称での発表となった。

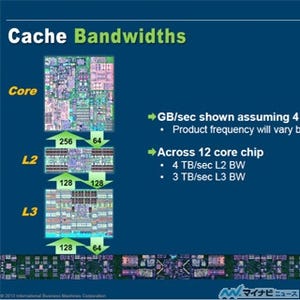

昨年の発表はプロセサコアのアーキテクチャに焦点を絞ったものであったが、今年のHot Chips 25では、キャッシュまわりを中心としたプロセササブシステムに関する発表が行われた。

|

|

zEC12メインフレームのプロセササブシステムについて発表するIBMのRobert Sonnelitter氏 |

名機System 360の流れを引く新世代メインフレーム「zEC12」

IBMのzEC12は、歴史的な名機であるSystem 360の流れを引くメインフレームの最新世代のマシンである。発表者のRobert Sonnelitter氏が、発表の冒頭で、メインフレームを使ったことのある人は手をあげてと言うと、挙手した人はまばらであった。しかし、最近、クレジットカードを使ったことが有る人と聞くと、当然ながら、大部分の人が手を上げた。そこで、Sonnelitter氏は、クレジットカードの決済はメインフレームで行われており、クレジットカードを使った人は、間接的にメインフレームを使っていると説明した。

このように、メインフレームコンピュータを、人々が意識して使うことは殆どないが、企業、特に金融関係ではメインフレームは健在である。

このような分野では、コンピュータ使用の長い歴史があり、膨大なプログラムがメインフレームに蓄積されている。メインフレームはx86ベースのLinuxサーバに比べると何倍も高いが、膨大なソフトウェア資産をx86 Linuxに移植してテストするコストに比べれば、ハードウェアのコストは微々たるもので、メインフレームを使い続けるほうが安上がりになる。また、長い歴史で培われた高信頼性は、x86 Linuxサーバをまだまだ寄せ付けない。

そして、クレジットカードの決済のような処理量は、年々増えていくので、より高性能な新機種の需要が生まれるというわけである。

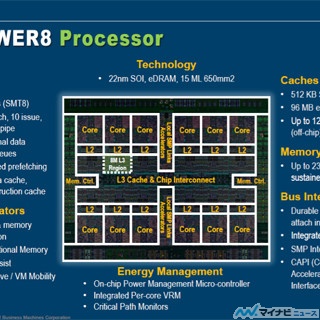

POWER8コアよりも大きいサイズとなったzEC12のコア

昨年の発表で、zEC12のCP(Central Processor)チップの概略のフロアプランは公表されていたが、今年はチップ写真が公開された。CPチップの製造プロセスはIBMの32nmプロセスで、チップサイズは598平方mmとなっている。昨年の発表では597平方mmであったが、量産版では少し大きくなったのかも知れない。

CPチップは6個のコアとeDRAMで作られた48MBの全コア共通のL3キャッシュを搭載している。また、チップの左の辺にはメモリコントローラとメモリインタフェースのIO、右の辺には周辺装置を接続するGXバスのコントローラとインタフェースが置かれている。そして、コアとL3キャッシュの間にCPチップ間を接続するためのインタフェース部分が置かれている。

このチップ写真から推測すると、各コアの面積は約56平方mmである。なお、巨大と言われるPOWER8のコア(512KBのL2$含まず)は16平方mmであり、プロセスが22nmと32nmと言う違いを補正しても、zEC12のコアはPOWER8コアの1.65倍のサイズである。

zEC12のコアは、専用の1MBの命令キャッシュと1MBのデータキャッシュを内蔵しているので、サイズが大きくなっているのではないかと思われる。

そして、アーキテクチャ的にシングルスレッド性能重視の設計で、L1命令キャッシュが64KB、L1データキャッシュが96KB、L2命令キャッシュとL2データキャッシュは独立でそれぞれが1MBと、x86プロセサなどと比べて大量のキャッシュを持っている。

これに加えて、業界最高の5.5GHzのクロックで、命令を実行する。まさに、シングルスレッド性能を追及するプロセサである。

そして、zEC12のシステムを構成する部品となるMCM(Multi Chip Module)には、6個のCPチップと次の述べる2個のSCチップが搭載されている。そして、MCMからは6本のメモリ接続バスと周辺装置を接続する8本のGXバス、そしてマルチノードの大規模共通メモリシステムを構成するための3ペアのFBCポートが出ている。

CPチップ同様、巨大なサイズのSCチップ

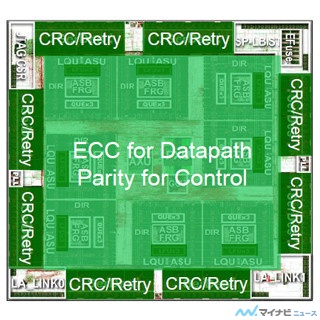

SCチップはCPチップと同様に32nmのSOIプロセスで製造され、これも526平方mmとかなり大きなチップである。このチップ写真を見ると、チップの大部分が192MBのeDARMのL4キャッシュで占められており、中央にちんまりと制御ロジックがあり、その周りをキャッシュディレクトリが取り囲むというレイアウトになっている。

そして、SCチップは6個のCPチップとの接続ポートと3つの他のMCMとの接続ポートを持っており、これらのポートのドライバとレシーバがチップの周辺を囲んでいる。

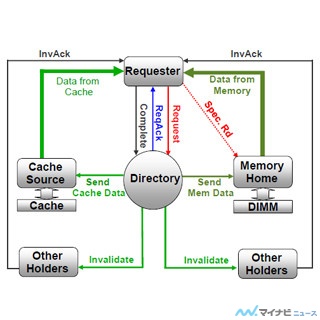

そして、MCMのブロック図は、つぎのようになっている。2個のSCチップから、6個のそれぞれのCPチップに直結の接続があり、L4キャッシュは、物理的には2個のSCチップに入っているが、論理的には1つの384MBのL4キャッシュとして動作する。また、L4キャッシュはディレクトリを持ち、システム全体のキャッシュコヒーレンシ制御を行っている。

MCMからは3ペアのSMP接続ポートが出ており、これで4つのMCMの間を完全結合で接続する。そうすると、120ソケットのシステムが出来上がるのであるが、IBMのメインフレームでは16個のCPをSystem Assist Processor、1個のCPをIntegrated Firmware Processorとして使い、2個のCPを故障時のスペアとして残しているので、ユーザが使えるCPの数は最大101個となっている。