Alteraは11月16日、次世代のSoC FPGAとしてハイエンドにIntel 10nmプロセスを採用する方針であるほか、価格要求や電力要求の厳しいローエンド向けにTSMCのプロセスを採用することを明らかにした。

これは同社のSenior Director, Product Marketing SoC ProductsであるChris Balough氏が語ったもので、次世代SoC FPGAとして3つのラインアップで開発が進められることが示された。Stratix 10の後継に位置づけられるハイエンド製品の開発コード名は「Altera Sequoia」で、Intelの10nmプロセスを採用することで、1000万超のロジックエレメント(LE)を1ダイ上で実現するという。コア数についてはまだ非公開とし、「ARM Enterprise-class multicore CPU System」とだけコメントするに留めている。対象とするのは、クラウド&アクセラレーションやテラビットシステム、軍事向け通信などとしており、アドバンストRASなどの機能も搭載されるとしている。

Arria 10の後継に位置づけられるミドルレンジ製品の開発コード名は「Altera Oak」で、Intelの14nmプロセスを採用する。プロセッサには4コアの64ビットARM CPUを採用し、4.5G/5Gの無線通信やUHD/8Kブロードキャストビデオ、Industrial IoT(IIoT)、自動車などとしている。そして低消費電力や低コストが求められる自動車やIIoT、スモールセル基地局などを対象としたCyclone Vの後継となるローエンド製品の開発コード名は「Altera Cedar」で、TSMCのプロセスを継続して採用していくことが予定されている。Altera Cedarの採用プロセスについては、「電力とコストを重視して設計されるため、必ずしも最先端のプロセスを使うとは限らない。両者のバランスを見て考える」(同)とするに留めた。こちらは2コアの64ビットARM CPUが搭載される予定だという。ちなみに同社では、この3つの開発コード名の頭文字を取ると「SoC」になるとしているが、3シリーズが同時に提供を開始する、ということはないとしている。

|

|

次世代SoC FPGAの概要。これまでのStratix、Arria、Cycloneの流れを汲む3つのシリーズが計画されている。共通部分も多いが、プロセスがすべて異なるなど、差異化が図られている部分も見受けられる。なお、詳細については、改めて説明する場を今後、設ける予定とのこと |

また、こうした製品を開発していく背景として同氏は「カスタマニーズの変化」、「半導体ビジネスの経済性」、「新技術への対応」の3つが組込業界に影響を与えるようになってきているため、と説明。そうした変化への対応をAlteraが積極的に進めている証拠と強調した。「組込業界もシングルコアからマルチコア、そしてヘテロジニアス化が進もうとしている。しかし、ASSPやASICは微細化が進めば進むほど、開発コストは増大するが、それだけの数を出荷できる市場はごくわずかで、組込機器ベンダは戦い方を変えなければならない。だからこそ我々はFine-Grained Heterogeneous Computingを標榜し、(ARMが掲げるbig.LITTLEのような)ヘテロジニアスなコンピューティングにFPGAのファブリックを提供することで、そうした変化への対応を促そうとしている」(同)とのことで、中でも自動車やロボット、産業機器分野で強みを持つ日本は非常に重要な市場になるとする。

Alteraは現在、Intelが買収を行ったため、事業統合に向けた作業が進められている。そうした中でAlteraとしては引き続き、FPGAビジネスを推進し、ARMコアを活用していくこととなる。「Intelの買収発表以降、ARMへの取り組みは今後どうなる、という問い合わせを多くの人から受けてきた。今回のARMコアを採用した次世代SoC FPGAを開発しているというアナウンスは、そうした問いに答えるものだ。確かにIntelの買収により、ビジネスはより強固なものとなる。Intelとしても、公にAlteraのARMへの取り組みをサポートし、進化させていくとしており、今後もこの流れに変更はない」と同氏は、今後もAlteraがSoC FPGAにコミットしていくとしたほか、「今後とももっとも強い、優れた長期的なサプライヤとして、カスタマのニーズに対応していくことを信頼してもらいたい」とし、半導体業界が変化を遂げていく中でAlteraが良いポジションにおり、今後もさまざまな機能の統合に向けた開発を継続し、ニーズに応えられる製品群を網羅していくとした。

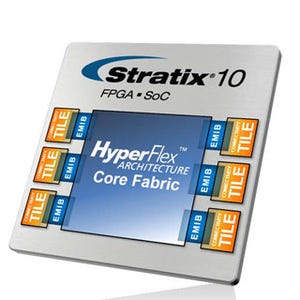

なおIntelの14nm Tri-Gateプロセスを採用したStratix 10では、オプション的にHBM2 DRAMと統合した「ヘテロジニアス SiPデバイス(Stratix 10 DRAM SiP)」などが発表されているが、次世代SoC FPGAでもそういった製品ラインアップが存在するのかどうかは現時点では非公開となっている。ただし、「まだ何も言えないが、IntelのEMIB(Embedded Multi-Die Interconnect Bridge)テクノロジーを活用することができるので、色々な可能性があると考えている」としており、単に先端プロセスを用いて大容量のLEを搭載したSoC FPGAが出る、というだけで終わることはないようだ。