2020年のHot Chipsは新型コロナウイルスの感染抑制のため、バーチャル開催ということになった。その代わり、参加費が200ドル以下と例年よりも大幅に割り引かれたので、開催2日目の数字であるが、出席者が2294人と2019年比で2倍程度になり、参加者数は断トツの新記録となった。

なお、今年の論文発表の申し込みは88件で、採択されて今回発表が行われた論文は25件となっている。採択率は28.4%であり、この比率は例年並みである。

10年周期で訪れるテクノロジ主導の大きな飛躍

例年、Hot Chipsの初日はチュートリアルで、2日目と3日目が本会議ということになる。そして、2日目と3日目には、一般発表に加えて基調講演が行われる。今回の2日目の基調講演を行ったのはIntelの上級副社長兼チーフアーキテクトで、アーキテクチャ、グラフィックスとソフトウェアのジェネラルマネージャーのRaja Koduri氏である。

Koduri氏は、次の図のように10年あまりの周期で、テクノロジ主導の大きな飛躍が起こっているという。1980年頃には全ての情報のデジタル化が起こり、1990年を過ぎたあたりで、全ての情報がネットワークでアクセスできるようになり、2010年の前には全ての情報がモバイルでアクセスできるようになった。そして、現在ではすべてがクラウドで処理される時代になっているという。

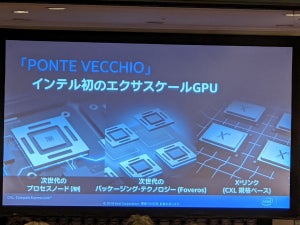

そして、この先は1000億台のインテリジェントなデバイスがネットワークで結合される時代となり、全てがインテリジェントになる時代が来るとKoduri氏は予想する。それは、誰もがExaスケールの処理能力を使える時代であるという。

なお、Intelの新しいグラフィックスアーキテクチャはXeと名付けられているがこれはエクサを誰も(Everyone)が使えるという命名であるという。

-

ほぼ10年ごとに不連続な大きなテクノロジの進化が起こり、それに導かれて社会の進歩が起こってきている。次の進化は全てのものがインテリジェントになり、誰もがエクサスケールの計算能力を使えるようになるという

どこまでも求められるコンピューティングパワー

2010年頃までは、ムーアの法則にしたがい2年で処理能力が2倍になる時代であった。しかし、ニューラルネットの幕開けのAlex-Netから、GoogleのAlphaGo Zeroまでの期間には30万倍の計算能力が必要とされるようになっている。これは必要な計算能力が3.4カ月で倍増する時代に入ったことを意味している。

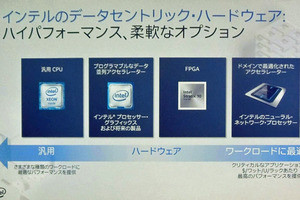

ただし、性能と汎用性とは反比例する関係があり、例えばチェス用に限定すれば人間のチャンピオンを凌ぐ人工知能が作れるが、汎用のロボットの頭脳を作るのはその何千倍も性能が必要になるという違いがあるという。

トランジスタ密度は5年で2倍程度にしかならず、ムーアの法則は息切れのように見られているが、ソフトウェアの性能向上なども含めて考えると、まだまだ、大きな性能向上の余地はある。

ソフトウェアの生産性は、ハードウェアの効率を大きく上回っており、Pythonプログラムに比べてC言語化では47倍の生産性向上になっている。これに並列化やベクトル化、さらにAVX命令の使用などによる、ハードウェアの効率向上を合わせて考えると、性能は6万3000倍に向上している。

-

ソフトウェアの生産性と、ハードウェアの効率を組み合わせて考えると、Pythonに比べて並列ループ化で7000倍程度の性能向上が得られ、それにベクトル化、AVX命令を組み合わせると、性能向上は6万3000倍になっている

マシンラーニングの場合でも、1年半のソフトウェアの改善で、推論の時間が秒単位であったものがミリ秒単位に短縮され、学習時間は週単位から時/分単位に短縮されている。

Koduri氏の親友で、AMDやIntelでの在籍時期もオーバラップしている天才エンジニアのJim Keller氏は、「There is still plenty of room at the bottom」と指摘していたという。