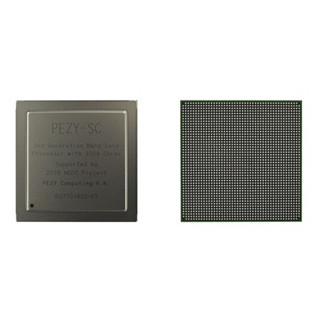

9月5日にPEZY Computingが、1024コアのPEZY-SCの完成と事業開始を発表した。1チップで単精度浮動小数点演算性能は3TFlops、倍精度浮動小数点演算性能は1.5TFlopsという高性能のプロセサを、殆どの人は聞いたこともない日本のベンチャー企業が開発したというのは驚きである。

ということで、同社の齊藤社長を直撃して、この驚異のプロセサの開発について聞いてみた。プレスリリースにも書かれているが、PEZYという社名は、Peta、Exa、Zetta、Yottaという1015、1018、1021、1024を表す国際単位系の接頭辞の頭文字を並べて名付けられている。これは、今後40~60年にわたって、高性能プロセサを開発していくという同社の姿勢を表すものであるという。

齊藤社長は、医師免許と医学博士(生体物理医学)の学位を持ち、1997年にシリコンバレーにTeraReconを設立し、1998年には世界初のリアルタイムに毎秒20フレームで手術中のCT画像を表示するシステムの開発に成功している。なお、齊藤社長はすでに同社を離れているが、TeraReconは、現在も医用画像処理のビジネスを続けている。

しかし、このような処理にはプロセサの性能が重要であるとの認識から、プロセサを開発する会社として2010年に日本でPEZY Computingを創立したという。PEZYは、NEDO(独立行政法人新エネルギー・産業技術総合開発機構)の助成金を得て、2012年4月に512コアのPEZY-1の開発に成功しており、PEZY-1を使ったPCIボードなどの販売やこのボードを使うシステムの受託開発などを行っているという。

そして、2012年には、1024コアのプロセサの開発提案がNEDOの戦略的省エネルギー技術革新事業に採択され、PEZY-SCの開発に着手した。そして、今回、開発に成功し、プレスリリースを出したという訳である。

PEZY社の現在の社員は、わずか16名で、齊藤社長を含めても技術者は12名という。当然、色々な協力会社があるが、それでも12名の技術者で1024コアのプロセサを設計、開発するのは驚異的である。

PEZYの第2世代のプロセサであるPEZY-SCのSCはSuper ComputerのSCであり、省電力コアを1024個搭載して演算性能を高めている。PEZY-SCを733MHzのクロックで動作させた場合の消費電力は60Wとのことである。ピーク演算性能は、単精度浮動小数点では3TFlops、倍精度浮動小数点では1.5TFlopsであり、チップ単体では単精度は50GFlops/W、倍精度は25GFlops/Wという高いエネルギー効率となっている。

ただし、実際のシステムでは、メモリやPCI Expressスイッチの消費電力、DC-DCコンバータの変換損失、さらに、サーバマザーボードの消費電力が加わるので、システムとしてのエネルギー効率はこれよりも低くなり、倍精度1ExaFlopsを40MWで実現できるわけではない。

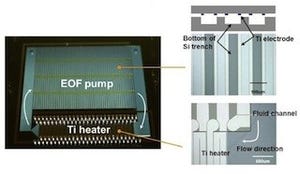

次の図は、PEZY-SCチップのブロック図であるが、下側の図がチップ全体のブロック図で、上の絵は一部の拡大図である。

PEZY-SCチップは4つの大きなブロックと、下側に描かれた8チャネルのDDR3/4コントローラ、そして右側に描かれた4チャネルのPCI Express Gen3×8ポートと2個のARM926コアから構成されている。

4つの大きなブロックはPrefecture(県)と呼ばれ、16個のCity(市)と共用の2MBのL3キャッシュからなっている。Cityは上の拡大図のように、4個のVillage(村)と64KBの共用L2キャッシュとSFU(特殊演算ユニット)から構成されている。そしてVillageは4個のPE(Processor Element)から構成されており、2PEごとに2KBのL1 Dキャッシュを持つ。なお、この図では省略されているが、City単位に32KBのL2Iキャッシュ、Prefecture単位に128KBのL3Iキャッシュを持っている。